# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 107290913 A (43)申请公布日 2017.10.24

(21)申请号 201710646087.3

(22)申请日 2017.07.31

(71)申请人 武汉华星光电技术有限公司 地址 430070 湖北省武汉市东湖开发区高 新大道666号生物城C5栋

(72)发明人 陈辰

(74)专利代理机构 深圳市威世博知识产权代理 事务所(普通合伙) 44280

代理人 钟子敏

(51) Int.CI.

GO2F 1/1362(2006.01) GO2F 1/1333(2006.01)

权利要求书1页 说明书6页 附图5页

## (54)发明名称

显示面板、阵列基板及其形成方法

#### (57)摘要

本发明公开了一种显示面板、阵列基板及其 形成方法。该阵列基板包括多个像素区域,每个 像素区域包括像素电极以及至少一个氧化物薄 膜晶体管,其中,像素电极的输入端与氧化物薄 膜晶体管的输出端连接,氧化物薄膜晶体管的控 制端与扫描线连接,扫描线的一端与驱动电路相 连接,氧化物薄膜晶体管还包括设置在其栅极上 的栅极绝缘层,其中,栅极绝缘层的厚度与对应 栅极所连接的扫描线,从驱动电路的连接点到栅 极连接点的长度成反比。通过上述实施方式,改 善了显示面板的均一性问题,提高显示面板的质量。

- 1.一种阵列基板,所述阵列基板包括多个像素区域,每个所述像素区域包括像素电极以及至少一个氧化物薄膜晶体管,其中,所述像素电极的输入端与所述氧化物薄膜晶体管的输出端连接,所述氧化物薄膜晶体管的控制端与扫描线连接,所述扫描线的一端与驱动电路相连接,其特征在于,所述氧化物薄膜晶体管还包括设置在其栅极上的栅极绝缘层,其中,所述栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述驱动电路的连接点到所述栅极连接点的长度成反比。

- 2.根据权利要求1所述的阵列基板,其特征在于,所述栅极绝缘层是通过沿所述扫描线的延伸方向,透光量按照设定条件依次增大的光罩所形成。

- 3.根据权利要求1所述的阵列基板,其特征在于,所述栅极绝缘层上还覆盖有光阻层, 所述栅极绝缘层是通过蚀刻所述光阻层而形成。

- 4.根据权利要求1所述的阵列基板,其特征在于,所述氧化物薄膜晶体管还包括覆盖在 所述栅极绝缘层上的氧化物薄膜层,以及设置在所述氧化物薄膜层上的源极以及漏极,其 中所述源极和所述漏极以一沟道分隔开。

- 5.根据权利要求4所述的阵列基板,其特征在于,所述源极、所述漏极以及所述源极和 所述漏极未覆盖到的氧化物薄膜层上还覆盖有钝化层。

- 6.根据权利要求1所述的阵列基板,其特征在于,所述阵列基板还包括多条相互平行的数据线,所述氧化物薄膜晶体管的输入端连接至对应的数据线,为所述像素电极输入显示信号。

- 7.一种显示面板,其特征在于,所述显示面板包括权利要求1~6任一项所述的阵列基板,还包括与所述阵列基板相对设置的彩膜基板,以及设置在所述彩膜基板与所述阵列基板之间的液晶层。

- 8.一种阵列基板的形成方法,其特征在于,所述形成方法包括:

在基板上形成栅极;

在栅极上形成栅极绝缘层,其中,所述栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述扫描线与驱动电路的连接点到所述栅极连接点的长度成反比。

9.根据权利要求8所述的形成方法,其特征在于,所述在栅极上形成栅极绝缘层的步骤具体包括:

在所述栅极绝缘层上覆盖光阻层,其中,所述光阻层的厚度与从所述驱动电路的连接 点到所述栅极连接点的长度成反比;

对所述光阻层进行蚀刻,形成厚度与对应栅极所连接的扫描线,从所述驱动电路的连接点到所述栅极连接点的长度成反比的栅极绝缘层。

10.根据权利要求8所述的形成方法,其特征在于,所述在栅极上形成栅极绝缘层的步骤具体包括:

采用沿所述扫描线的延伸方向,透光量按照设定条件依次增大的光罩形成所述栅极绝缘层。

# 显示面板、阵列基板及其形成方法

#### 技术领域

[0001] 本发明涉及显示技术领域,特别是涉及一种显示面板、阵列基板及其形成方法。

## 背景技术

[0002] 薄膜晶体管液晶显示器 (Thin film Transistor-Liquid Crystal Display, 简称 TFT-LCD) 是目前主流的显示装置,其显示区由阵列基板上的无数个像素区域所组成。

[0003] TFT-LCD工作时,通过扫描线给TFT的栅极施加特定的电压,控制TFT的导通或断开。由于扫描线一般为金属层,从而存在一定电阻,随着信号传输距离的增加,扫描线信号会逐步削弱,这种现象称为压降,随着子像素与扫描线的驱动输入端的距离由近至远,压降效应会逐渐增加,导致靠近扫描线输入端的TFT的栅极输入电压比远离扫描线输入端的TFT的栅极输入电压要大,因此会造成靠近扫描线输入端的画面较亮,而远离扫描线输入端的画面较暗,影响了显示面板的显示均一性。

# 发明内容

[0004] 本发明主要解决的技术问题是提供一种显示面板、阵列基板及其形成方法,改善了显示面板的均一性问题,提高显示面板的质量。

[0005] 为解决上述技术问题,本发明采用的第一个技术方案是:提供一种阵列基板,所述阵列基板包括多个像素区域,每个所述像素区域包括像素电极以及至少一个氧化物薄膜晶体管,其中,所述像素电极的输入端与所述氧化物薄膜晶体管的输出端连接,所述氧化物薄膜晶体管的控制端与扫描线连接,所述扫描线的一端与驱动电路相连接,所述氧化物薄膜晶体管还包括设置在其栅极上的栅极绝缘层,其中,所述栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述驱动电路的连接点到所述栅极连接点的长度成反比。

[0006] 为解决上述技术问题,本发明采用的第二个技术方案是:提供一种显示面板,所述显示面板包括本发明任一项所述的阵列基板,还包括与所述阵列基板相对设置的彩膜基板,以及设置在所述彩膜基板与所述阵列基板之间的液晶层。

[0007] 为解决上述技术问题,本发明采用的第三个技术方案是:提供一种阵列基板的形成方法,所述形成方法包括:在基板上形成栅极;在栅极上形成栅极绝缘层,其中,所述栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述扫描线与驱动电路的连接点到所述栅极连接点的长度成反比。

[0008] 本发明的有益效果是:本发明的阵列基板中所包含的氧化物薄膜晶体管的栅极绝缘层的厚度与对应栅极所连接的扫描线,从扫面线与驱动电路的连接点到扫描线与栅极的连接点的长度成反比。而薄膜晶体管的栅绝缘层的厚度与寄生电容Cgs的大小成反比,因此可以降低了压降效应的影响,改善显示面板均一性问题,从而提高了显示面板的质量。

# 附图说明

[0009] 图1是本发明阵列基板一实施方式的结构示意图;

2/6 页

- [0010] 图2是图1阵列基板氧化物薄膜晶体管的一实施方式的结构示意图;

- [0011] 图3是图1阵列基板的氧化物薄膜晶体管另一实施方式的结构示意图:

- [0012] 图4是图1阵列基板像素区域一实施方式的电路示意图;

- [0013] 图5是本发明显示面板一实施方式的结构示意图;

- [0014] 图6是本发明阵列基板的形成方法一实施方式的流程示意图:

- [0015] 图7是图6阵列基板的形成方法一实施方式的结构示意图;

- [0016] 图8是图6阵列基板的形成方法另一实施方式的结构示意图:

- [0017] 图9是图6阵列基板的形成方法又一实施方式的结构示意图。

# 具体实施方式

[0018] 本发明提供一种显示面板、阵列基板及其形成方法,为使本发明的目的、技术方案 和技术效果更加明确、清楚,以下对本发明进一步详细说明,应当理解此处所描述的具体实 施条例仅用于解释本发明,并不用于限定本发明。

本实施方式提供一种阵列基板,该阵列基板包括多个像素区域,每个像素区域包 括像素电极以及至少一个氧化物薄膜晶体管。阵列基板还包括多条相互平行的数据线,氧 化物薄膜晶体管的输入端连接至对应的数据线,为像素电极输入显示信号。其中,像素电极 的输入端与氧化物薄膜晶体管的输出端连接,氧化物薄膜晶体管的控制端与扫描线的一端 连接,扫描线的另一端与驱动电路相连接。

其中,前述驱动电路为可以提供特定电压的电路,通过扫描线向氧化物薄膜晶体 [0020] 管的控制端写入相应的电压,控制氧化物薄膜晶体管的通断。

在其中一个实施方式中,氧化物薄膜晶体管为底栅型结构,氧化物薄膜晶体管包 括栅极,还包括设置在栅极上的栅极绝缘层和覆盖在栅极绝缘层上的氧化物薄膜层以及设 置在氧化物薄膜层上的源极以及漏极,且源极和漏极以一沟道分隔开。而且,在源极、漏极 以及源极和漏极未覆盖到的氧化物薄膜层上还覆盖有钝化层。

[0022] 可选地,在另一个实施方式中,氧化物薄膜晶体管也可以是顶栅型结构,即氧化物 薄膜晶体管包括源极以及漏极、设置在源极以及漏极上的栅极绝缘层以及设置在栅极绝缘 层上的栅极。氧化物薄膜晶体管的类型可以根据情况设计,在此不做具体限定。

需要说明的是,不论氧化物薄膜晶体管是顶栅型结构还是底栅型结构,栅极绝缘 层的厚度与对应栅极所连接的扫描线,从扫描线与驱动电路的连接点到扫描线与对应栅极 的连接点之间的长度成反比。

另外,每个像素区域的氧化物薄膜晶体管的数目也可以是2个或3个,可根据实际 情况设计,在此不做具体限定。

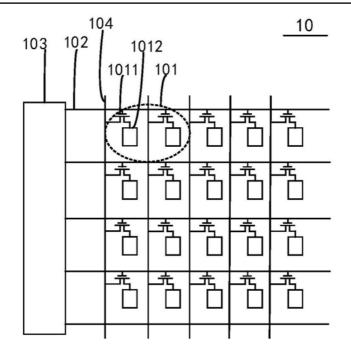

[0025] 为了清楚的说明上述阵列基板的结构,参阅图1,图1是本发明阵列基板一实施方 式的结构示意图。

在本实施方式中,阵列基板10包括多条平行的扫描线102和多条平行的数据线 104。其中,扫描线102和数据线104的总数目不做具体限定,可根据实际情况设计。扫描线 102与数据线104相互交叉但不相交组成多个像素区域101,其中,像素区域101包括氧化物 薄膜晶体管1011和像素电极1012。氧化物薄膜晶体管1011的输出端与像素电极1012的输入 端连接,氧化物薄膜晶体管1011的控制端与扫描线102的一端连接,扫描线102的另一端与 驱动电路103连接。

[0027] 其中,氧化物薄膜晶体管1011包括栅极和栅极绝缘层,栅极绝缘层的厚度与对应栅极所连接的扫描线102,从扫描线102与驱动电路103的连接点到扫描线102与对应氧化物薄膜晶体管1011的栅极的连接点之间的长度成反比。

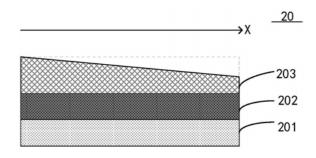

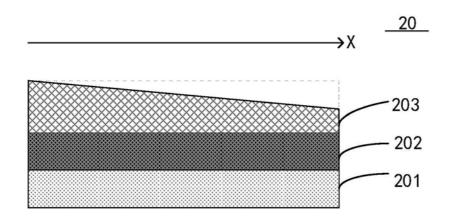

[0028] 具体地,为了清楚的说明阵列基板中氧化物薄膜晶体管的的栅极绝缘层的厚度与对应栅极所连接的扫描线,从扫描线与驱动电路的连接点到扫描线与对应氧化物薄膜晶体管的栅极的连接点之间的长度成反比,参阅图2,图2是图1阵列基板氧化物薄膜晶体管的一实施方式的结构示意图。

[0029] 其中,阵列基板20中的氧化物薄膜晶体管包括基板201、设置在基板201上的氧化物薄膜晶体管的其他膜层202、以及设置在氧化物薄膜晶体管的其他膜层202上的栅极绝缘层203。图2中箭头X所指的方向为阵列基板20扫描线的延展方向,即从扫描线与驱动电路的连接点到扫描线与对应氧化物薄膜晶体管的栅极的连接点所指的方向。沿着箭头X的方向,扫描线与对应氧化物薄膜晶体管的栅极的连接点与扫描线与驱动电路的连接点之间的长度逐渐增大,对应氧化物薄膜晶体管栅极绝缘层203的厚度逐渐减小,即成反比关系。

[0030] 在此,需要强调的是,图2所示的氧化物薄膜晶体管是阵列基板中部分氧化物薄膜晶体管的整体结构示意图,用于表征,本实施方式中与同一条扫描线连接的不同氧化物薄膜晶体管的栅极绝缘层的厚度不同。

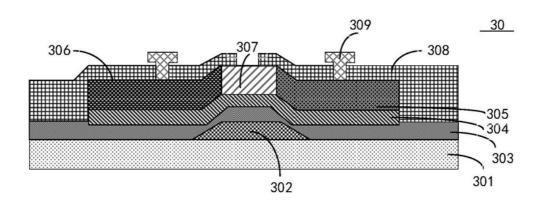

[0031] 为了清楚的说明上述实施例的氧化物薄膜晶体管的结构,以底栅型结构的氧化物薄膜晶体管为例说明,参阅图3,图3是图1阵列基板的氧化物薄膜晶体管另一实施方式的结构示意图。

[0032] 在本实施方式中,氧化物薄膜晶体管30包括基板301、栅极302、设置在栅极302上的栅极绝缘层303、覆盖在栅极绝缘层303上的氧化物薄膜层304、设置在氧化物薄膜层304上的源极305以及漏极306,其中,源极305和漏极306被一沟道307隔开,覆盖在源极305、漏极306、所述源极305和所述漏极306未覆盖到的氧化物薄膜层304上钝化层308以及设置在钝化层308上接触电极309。

[0033] 在其中的一个实施方式中,阵列基板包含氧化物薄膜晶体管30,阵列基板还包含扫描线和驱动电路,扫描线的一端与驱动电路连接,扫描线的另一端与若干个氧化物薄膜晶体管30的控制端栅极302连接,其中,与同一条扫描线连接的氧化物薄膜晶体管30的栅极绝缘层303的厚度与对应栅极302所连接的扫描线,从扫描线与驱动电路的连接点到扫描线与对应栅极302的连接点之间的长度成反比。

[0034] 进一步地,栅极绝缘层303可以是通过沿扫描线的延伸方向,透光量按照设定条件依次增大的光罩所形成。具体地,可通过在栅极绝缘层303上覆盖光阻层,通过透光量按照设定条件依次增大的掩膜板定义栅极绝缘层303的图形,再通过蚀刻所述光阻层而形成。在另一个实施方式中,也可以通过沿扫描线的延伸方向,光强依次增大的入射光进行光罩而形成。

[0035] 在此,需要强调的是,图3中所示的氧化物薄膜晶体管30是单个氧化物薄膜晶体管30的具体结构示意图,用于解释本实施方式中氧化物薄膜晶体管30的具体膜层之间的结构。

[0036] 在实际情况下,制造阵列基板时由于工艺制成的限制,氧化物薄膜晶体管会存在

寄生电容 $C_{gs}$ ,而寄生电容 $C_{gs}$ 的大小与氧化物薄膜晶体管的栅极绝缘层的厚度有关。在使用显示装置的时候,由于寄生电容 $C_{gs}$ 的存在使显示装置出现显示的亮度不均匀的问题。

[0037] 上述实施方式的阵列基板中氧化物薄膜晶体管的栅极绝缘层的厚度不相同,使得氧化物薄膜晶体管的寄生电容C<sub>ss</sub>不相同,从而可以改善显示的均一性问题。

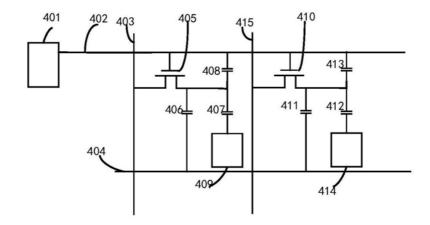

[0038] 为了详细的解释通过设计栅极绝缘层的厚度改善显示的均一性问题的工作原理, 参阅图4,图4是图1阵列基板像素区域一实施方式的电路示意图。

[0039] 如图4所示,在本实施方式中,像素区域包括氧化物薄膜晶体管405和氧化物薄膜晶体管410,氧化物薄膜晶体管405和氧化物薄膜晶体管410的对应栅极与同一条扫描线402的一端连接,扫描线402的另一端与驱动电路401连接。

[0040] 氧化物薄膜晶体管405的漏极与数据线403连接,氧化物薄膜晶体管405的源极与存储电容 $C_{\rm st}$ 406和像素电容 $C_{\rm lc}$ 407的一端连接,存储电容 $C_{\rm st}$ 406的另一端与公共电极端404连接,像素电容 $C_{\rm lc}$ 407的另一端与像素电极409连接。同时,氧化物薄膜晶体管405的栅极与源极和漏极之间存在寄生电容 $C_{\rm gs}$ 408。

[0041] 氧化物薄膜晶体管410的漏极与数据线415连接,氧化物薄膜晶体管410的源极与存储电容 $C_{\rm st}$ 411和像素电容 $C_{\rm lc}$ 412的一端连接,存储电容 $C_{\rm st}$ 411的另一端与公共电极端404连接,像素电容 $C_{\rm lc}$ 412的另一端与像素电极414连接。同时,氧化物薄膜晶体管410的栅极与源极和漏极之间存在寄生电容 $C_{\rm gs}$ 413。

[0042] 需要说明的是,由于氧化物薄膜晶体管410的栅极与扫描线402的连接点与扫描线402与驱动电路401的连接点之间的长度比氧化物薄膜晶体管405的栅极与扫描线402的连接点与扫描线402与驱动电路401的连接点之间的长度要大,故按照上述实施方式形成氧化物薄膜晶体管410的栅极绝缘层的厚度比按照上述实施方式形成氧化物薄膜晶体管405的栅极绝缘层的厚度要小。因此,寄生电容Cgs413比寄生电容Cgs408大。

[0043] 阵列基板在工作时,通过扫描线402给氧化物薄膜晶体管405和氧化物薄膜晶体管410的对应栅极施加特定的电压V<sub>gh1</sub>控制氧化物薄膜晶体管405和氧化物薄膜晶体管410的通断。由于扫描线402一般为金属层,从而存在一定电阻,随着信号传输距离的增加,扫描线402信号会逐步削弱,这种现象称为压降,对应压降的理论计算公式为

$$\Delta V_{_{p}} \,=\, \frac{C_{_{gs}}}{C_{_{gs}}\,+\,C_{_{Ic}}\,+\,C_{_{st}}} *\,V_{_{ghI}} \ (\,\triangle\,\pounds\,1\,) \ . \label{eq:deltaVp}$$

[0044] 由于寄生电容 $C_{gs}413$ 比寄生电容 $C_{gs}408$ 大,存储电容 $C_{st}406$ 和存储电容 $C_{st}411$ 大 小相等,像素电容 $C_{1c}407$ 和像素电容 $C_{1c}412$ 大小相等。根据

$$\Delta V_p = \frac{C_{gs}}{C_{gs} + C_{lc} + C_{st}} * V_{ghl}$$

(公式 1)的压降效应计算方法可以得知,寄生电容

Cgs413比寄生电容Cgs408大且满足相应的比例时,传导到氧化物薄膜晶体管405的栅极的电压与传导到氧化物薄膜晶体管410的栅极的电压相等,从而可以改善显示的均一性问题。其中,相应的比例需要根据具体情况设计,在此不做具体限定。

[0045] 区别现有技术,本实施方式的阵列基板中所包含的氧化物薄膜晶体管的栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述驱动电路的连接点到栅极连接点的长度成反比。而氧化物薄膜晶体管的栅绝缘层的厚度与寄生电容Cgs的大小成反比,因此可以降低了

压降效应的影响,改善显示面板均一性问题,从而提高了显示面板的质量。

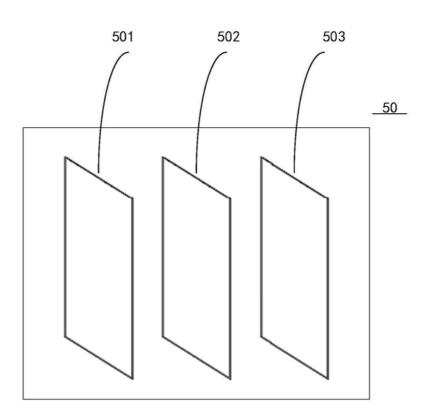

[0046] 在另一个实施方式,参阅图5,图5是本发明显示面板一实施方式的结构示意图,显示面板50包括本发明任一所述的阵列基板502,还包括与阵列基板502相对设置的彩膜基板501和彩膜基板503,以及设置在彩膜基板与阵列基板之间的液晶层。

[0047] 关于阵列基板502的结构前述已详尽描述,在此不再赘谈。

[0048] 区别现有技术,本实施方式的阵列基板中所包含的氧化物薄膜晶体管的栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述驱动电路的连接点到栅极连接点的长度成反比。而氧化物薄膜晶体管的栅绝缘层的厚度与寄生电容Cgs的大小成反比,因此可以降低了压降效应的影响,改善显示面板均一性问题,从而提高了显示面板的质量。

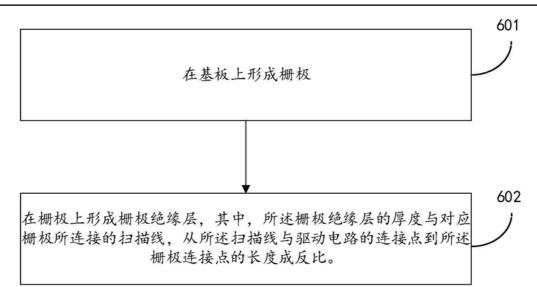

[0049] 在又一个实施方式中,参阅图6,图6是本发明阵列基板一实施方式的形成方法的流程示意图。

[0050] 601:在基板上形成栅极。

[0051] 在本实施方式中,通过光罩显影或蚀刻在基板上形成栅极。

[0052] 602:在栅极上形成栅极绝缘层,其中,所述栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述扫描线与驱动电路的连接点到所述栅极连接点的长度成反比。

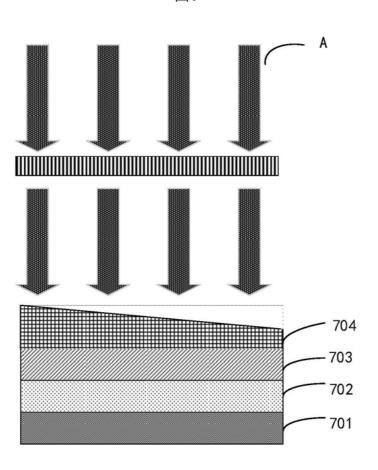

[0053] 在其中的一个实施方式中,参阅图7,图7是图6阵列基板的形成方法一实施方式的结构示意图。

[0054] 如图7所示,在基板701上形成栅极702,在栅极702上覆盖薄膜703,在薄膜703上覆盖光阻层704,该光阻层704的厚度与从驱动电路的连接点到栅极连接点的之间的长度成反比。通过光强一样的入射光A对光阻层704进行光罩。再对光阻层704进行蚀刻,从而形成厚度与对应栅极所连接的扫描线,从驱动电路的连接点到栅极连接点的长度成反比的栅极绝缘层。

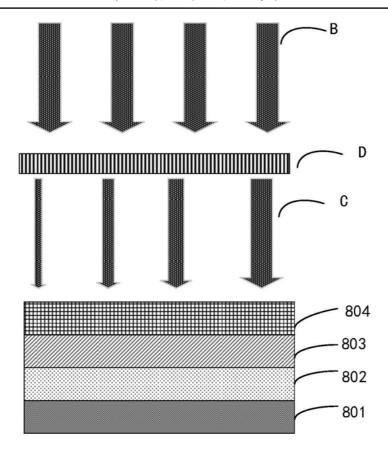

[0055] 在另一个实施方式中,参阅图8,图8是图6阵列基板的形成方法另一实施方式的结构示意图。

[0056] 如图8所示,在基板801上形成栅极802,在栅极802上覆盖薄膜803,在薄膜803上覆盖光阻层804,该光阻层804的厚度一样,采用沿着扫描线的延伸方向,使用透光量按照设定条件依次增大的光罩D对栅极绝缘层进行光罩,形成栅极绝缘层。如图8所示,入射光B的光强是一样的,透过光罩D之后的入射光C的光强沿着扫描线的方向依次增大。通过本实施方式形成的栅极绝缘层的厚度对应栅极所连接的扫描线,从驱动电路的连接点到栅极连接点的长度成反比的栅极绝缘层。

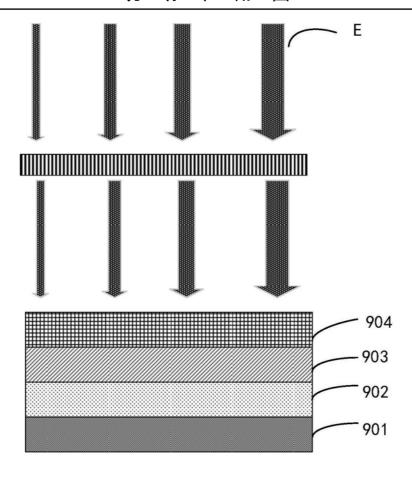

[0057] 可选地,在又一个实施方式中,参阅图9,图9是图6阵列基板的形成方法又一实施方式的结构示意图。

[0058] 如图9所示,在基板901上形成栅极902,在栅极902上覆盖薄膜903,在薄膜903上覆盖光阻层904,该光阻层904的厚度一样,对光阻层904进行光罩,其中入射光E的光强不一样,沿着扫描线的方向依次增大,通过本实施方式形成的栅极绝缘层的厚度对应栅极所连接的扫描线,从驱动电路的连接点到栅极连接点的长度成反比的栅极绝缘层。

[0059] 需要说明的是,上述任一实施方式可以相互结合从而形成与上述任一实施方式等效的栅极绝缘层,在此不再具体说明。

[0060] 进一步地,在一个实施方式,阵列基板中所包含薄膜晶体管为顶栅

[0061] 型结构时,也可以使用上述任一实施方式中的形成方法来制备。

[0062] 区别于现有技术,通过本实施方式的阵列基板的形成方法所形成的阵列基板中所包含的氧化物薄膜晶体管的栅极绝缘层的厚度与对应栅极所连接的扫描线,从所述驱动电路的连接点到栅极连接点的长度成反比。而氧化物薄膜晶体管的栅绝缘层的厚度与寄生电容Cgs的大小成反比,因此可以降低了压降效应的影响,改善显示面板均一性问题,从而提高了显示面板的质量。

[0063] 以上所述仅为本发明的实施方式,并非因此限制本发明的专利保护范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

图1

图2

图3

图4

图5

图6

图7

图8

图9