### (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10)授权公告号 CN 102130659 B (45)授权公告日 2013.03.13

(21)申请号 201110009728.7

审查员 白桦

- (22)申请日 2011.01.20

- (73) 专利权人 西安理工大学 地址 710048 陕西省西安市金花南路 5 号

- (72) 发明人 杨媛 杨晓菲

- (74) 专利代理机构 西安弘理专利事务所 61214 代理人 罗笛

- (51) Int. CI.

HO3F 3/45 (2006.01)

#### (56)对比文件

- CN 101841308 A, 2010. 09. 22, 全文.

- CN 101587699 A. 2009.11.25, 全文.

- US 6057734 A, 2000.05.02, 全文.

- US 6300834 B1, 2001.10.09, 全文.

权利要求书 1 页 说明书 5 页 附图 6 页

#### (54) 发明名称

一种减小两级运算放大器输入失调电压的电 路结构

#### (57) 摘要

本发明提供一种减小两级运算放大器输入失调电压的电路结构,包括交换控制电路、第一级差分放大电路、第二级共源放大电路以及补偿网络;交换控制电路的输出端与第一级差分放大电路的输入端连接,第一级差分放大电路的输入端连接,第二级共源放大电路的输入端与输出端之间还连接有补偿网络。其有益效果是,采用 MOS 开关管控制交换运放正负输入端信号和输出端信号来减小运放的失调,由于电路中只增加了 MOS 开关管,它们只需要很小的面积,极低的功耗,该电路在降低运算放大器输入失调电压的同时,不影响运放的增益,相位裕量,电源电压抑制比,共模输入范围等性能指标,可应用于主流 CMOS 电路系统中。

CN 102130659 B

1. 一种减小两级运算放大器输入失调电压的电路结构,其特征在于,包括交换控制电路(1)、第一级差分放大电路(2)、第二级共源放大电路(3)以及补偿网络(4);交换控制电路(1)的输出端与第一级差分放大电路(2)的输入端连接,第一级差分放大电路(2)的输出端与第二级共源放大电路(3)的输入端连接,第二级共源放大电路(3)的输入端与输出端之间还连接有补偿网络(4);

所述的交换控制电路(1)由4个PMOS管构成,分别为:第七PMOS管(m13)、第八PMOS管(m14)、第九PMOS管(m15)和第十PMOS管(m16);第七PMOS管(m13)和第八PMOS管(m14)的源端接输入信号in1,第九PMOS管(m15)和第十PMOS管(m16)的源端接输入信号in2;第八PMOS管(m14)和第九PMOS管(m15)的栅极分别接控制信号ck1,第七PMOS管(m13)和第十PMOS管(m16)的栅极分别接控制信号ck2;第八PMOS管(m14)和第十PMOS管(m16)的漏端相连接,其输出信号为ea1;第七PMOS管(m13)和第九PMOS管(m15)的漏端相连接,其输出信号为ea2。

2. 根据权利要求 1 所述的减小两级运算放大器输入失调电压的电路,其特征在于: 所述第一级差分放大电路(2)包括第一 NMOS 管(m1)、第二 NMOS 管(m2)、第三 NMOS 管(m5)、第四 NMOS 管(m7)、第五 NMOS 管(m8)、第一 PMOS 管(m3)、第二 PMOS 管(m4)、第三 PMOS 管(m9)、第四 PMOS 管(m10)、第五 PMOS 管(m11)和第六 PMOS 管(m12);

所述第二级共源放大电路(3)包括第七 PMOS 管(m6);

所述补偿网络(4)包括串联的消零电阻(R<sub>c</sub>)和补偿电容(C<sub>c</sub>);

第一PMOS 管(m3)、第二PMOS 管(m4)和第七PMOS 管(m6)三者的源端相连接并接工作电压;第一PMOS 管(m3)和第二PMOS 管(m4)的栅极连接;第一PMOS 管(m3)的漏端经过输出端 out1与第一NMOS 管(m1)的源端连接,第二PMOS 管(m4)的漏端经过输出端 out2与第二NMOS 管(m2)的源端连接;第一NMOS 管(m1)和第二NMOS 管(m2)的栅极分别接交换控制电路(1)的输出信号 ea1和交换控制电路(1)的输出信号 ea2,第一NMOS 管(m1)和第二NMOS 管(m2)的漏端连接并同时与第三NMOS 管(m5)的源端连接;第三NMOS 管(m5)、第五NMOS 管(m8)和第四NMOS 管(m7)的栅极连接,第三NMOS 管(m8)和第四NMOS 管(m7)的栅极连接,第三NMOS 管(m8)和第四NMOS 管(m7)的漏端连接并接地;第五NMOS 管(m8)的源端与栅极连接,并同时接工作电压;

第三 PMOS 管 (m9) 和第四 PMOS 管 (m10) 的源端分别接第一 PMOS 管 (m3) 与第二 PMOS 管 (m4) 的栅极,第三 PMOS 管 (m9) 和第四 PMOS 管 (m10) 的栅极分别接控制信号 ck2 和控制信号 ck1,其漏端分别接输出端 out1 和输出端 out2;第五 PMOS 管 (m11) 和第六 PMOS 管 (m12) 的源端分别接输出端 out1 和输出端 out2,其栅极分别接控制信号 ck1 和控制信号 ck2,第五 PMOS 管 (m11) 和第六 PMOS 管 (m12) 的漏端相连接并接输出端 out\*;输出端 out\*分别与消零电阻  $(R_z)$  的一端和第七 PMOS 管 (m6) 的栅极连接;第七 PMOS 管 (m6) 的漏端与第四 NMOS 管 (m7) 的源端连接;消零电阻  $(R_z)$  的另一端通过补偿电容  $(C_c)$  输出电压,补偿网络 (4) 还通过电容  $(C_c)$  接地。

## 一种减小两级运算放大器输入失调电压的电路结构

#### 技术领域

[0001] 本发明属于微电子学与固体电子学技术领域,涉及一种集成电路的运算放大器电路,具体涉及一种减小两级运算放大器输入失调电压的电路结构。

#### 背景技术

[0002] 运算放大器广泛应用于模拟电路及数模混合电路中。由于 CMOS 技术已经成为集成电路的主流技术,与传统双极型电路相比, CMOS 运算放大器电路在成本和开发周期上具有显著优势。现有减小运放失调电压电路设计思路为采用斩波技术和自动调零技术实现,但斩波技术需要将输入信号和开关型方波信号耦合,再经同步解调和低通滤波后得到非线性小的信号,电路复杂度增加,会明显增加电路面积;自动调零技术要将失调存储在电容中,主要有输入失调存储和输出失调存储,主要适用于开关电容等离散信号电路。因此设计出工艺与 CMOS 工艺相兼容且不降低运放其他性能的减小失调的电路结构具有重要的意义。

#### 发明内容

[0003] 本发明的目的是提供一种减小运算放大器输入失调电压的电路结构,以减小现有 CMOS 集成运放输入失调电压。

[0004] 本发明所采用的技术方案是,一种减小两级运算放大器输入失调电压的电路结构,包括交换控制电路、第一级差分放大电路、第二级共源放大电路以及补偿网络;交换控制电路的输出端与第一级差分放大电路的输入端连接,第一级差分放大电路的输出端与第二级共源放大电路的输入端连接,第二级共源放大电路的输入端与输出端之间还连接有补偿网络。

[0005] 其中,交换控制电路由 4个 PMOS 管构成,分别为:第七 PMOS 管、第八 PMOS 管、第九 PMOS 管和第十 PMOS 管;第七 PMOS 管和第八 PMOS 管的源端接输入信号 in1,第九 PMOS 管和第十 PMOS 管的源端接输入信号 in2;第八 PMOS 管和第九 PMOS 管的栅极分别接控制信号 ck1,第七 PMOS 管和第十 PMOS 管的栅极分别接控制信号 ck2;第八 PMOS 管和第十 PMOS 管的漏端相连接,其输出信号为 ea1;第七 PMOS 管和第九 PMOS 管的漏端相连接,其输出信号为 ea2。

[0006] 其中,第一级差分放大电路包括第一 NMOS 管、第二 NMOS 管、第三 NMOS 管、第三 NMOS 管、第三 NMOS 管、第三 NMOS 管、第三 PMOS 管、第三 PMOS 管、第四 PMOS 管、第五 PMOS 管 和第六 PMOS 管;第二级共源放大电路包括第七 PMOS 管;补偿网络包括串联的消零电阻和补偿电容;第一 PMOS 管、第二 PMOS 管和第七 PMOS 管三者的源端相连接并接工作电压;第一 PMOS 管和第二 PMOS 管的栅极连接;第一 PMOS 管的漏端经过输出端 out1 与第一 NMOS 管的源端连接,第二 PMOS 管的漏端经过输出端 out2 与第二 NMOS 管的源端连接;第一 NMOS 管和第二 NMOS 管的栅极分别接交换控制电路的输出信号 ea1 和交换控制电路的输出信号 ea2,第一 NMOS 管和第二 NMOS 管的漏端连接并同时与第三 NMOS 管的源端连接;第三 NMOS 管、第

五 NMOS 管和第四 NMOS 管的栅极连接,第三 NMOS 管、第五 NMOS 管和第四 NMOS 管的漏端连接并接地;第五 NMOS 管的源端与栅极连接,并同时接工作电压;第三 PMOS 管和第四 PMOS 管的源端分别接第一 PMOS 管与第二 PMOS 管的栅极,第三 PMOS 管和第四 PMOS 管的栅极分别接控制信号 ck2 和控制信号 ck1,其漏端分别接输出端 out1 和输出端 out2;第五 PMOS 管和第六 PMOS 管的源端分别接输出端 out1 和输出端 out2,其栅极分别接控制信号 ck1 和控制信号 ck2,第五 PMOS 管和第六 PMOS 管的漏端相连接并接输出端 out\*;输出端 out\*分别与消零电阻的一端和第七 PMOS 管的栅极连接;第七 PMOS 管的漏端与第四 NMOS 管的源端连接;消零电阻的另一端通过补偿电容输出电压,补偿网络还通过电容接地。

[0007] 本发明的有益效果是,采用 MOS 开关管控制交换运放正负输入端信号和输出端信号来减小运放的失调,由于电路中只增加了 MOS 开关管,它们只需要很小的面积,极低的功耗,该电路在降低运算放大器输入失调电压的同时,不影响运放的增益,相位裕量,电源电压抑制比 (PSRR),共模输入范围等性能指标,可应用于主流 CMOS 电路系统中。

#### 附图说明

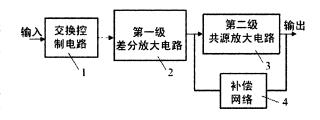

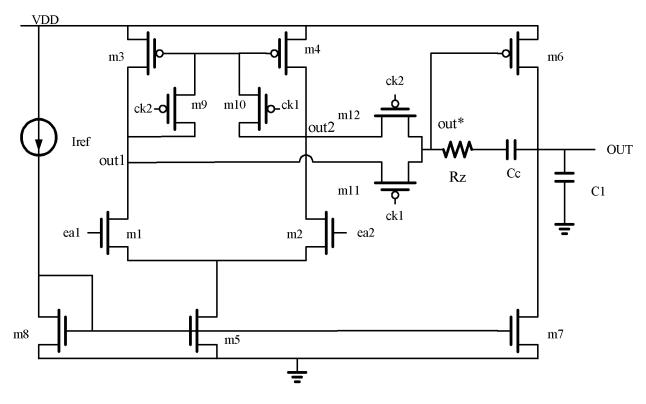

[0008] 图 1 是传统两级运算放大器的电路结构图;

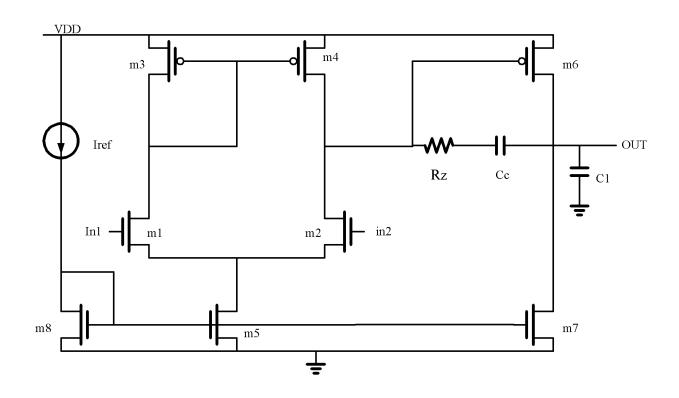

[0009] 图 2 是本发明两级运算放大器的结构框图;

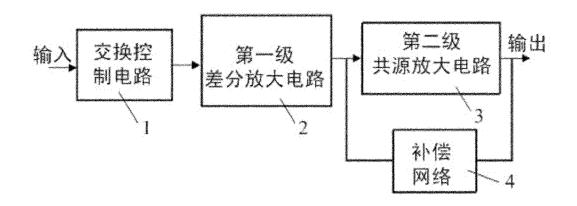

[0010] 图 3 是本发明电路中交换控制电路的电路图;

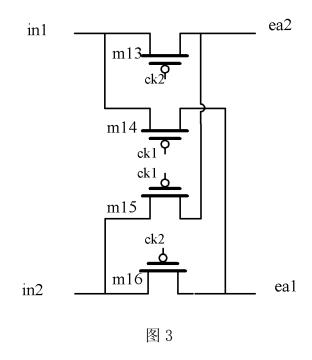

[0011] 图 4 是本发明的电路中两级运放的电路图;

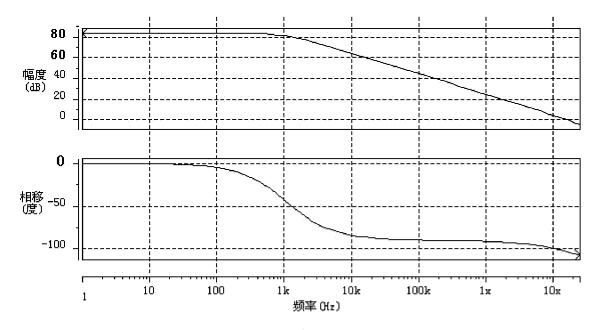

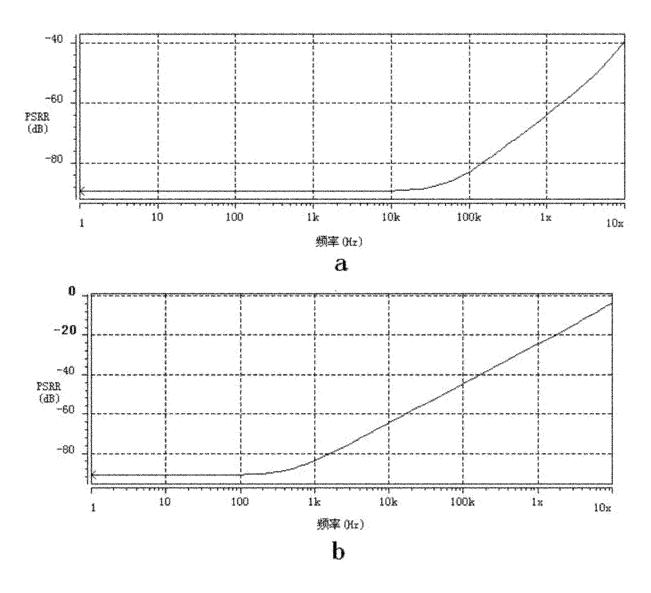

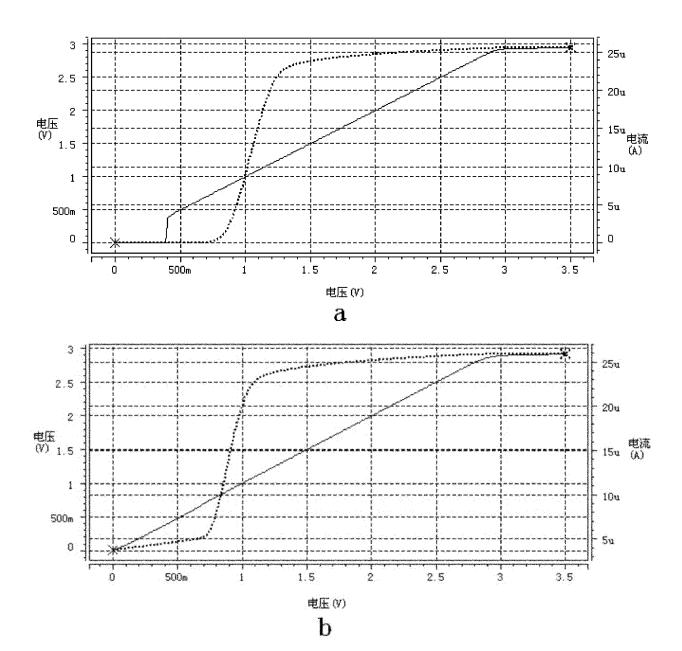

[0012] 图 5 是传统两级运算放大器电路与本发明运放电路的开环频率响应的仿真曲线对比图 (a 是传统的两级运算放大器电路的开环频率响应的仿真曲线图,b 是采用本发明的运放电路的开环频率响应的仿真曲线图):

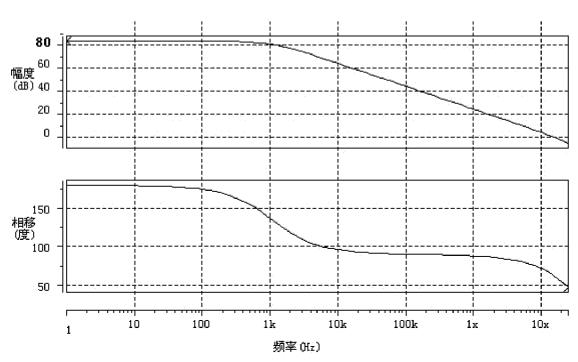

[0013] 图 6 是传统的两级运算放大器电路和采用本发明的运放电路的电源电压抑制比 PSRR 频率响应的仿真曲线对比图 (a 是传统两级运算放大器电路的电源电压抑制比 PSRR 频率响应的仿真曲线图, b 是本发明运放电路的电源电压抑制比 PSRR 频率响应的仿真曲线图);

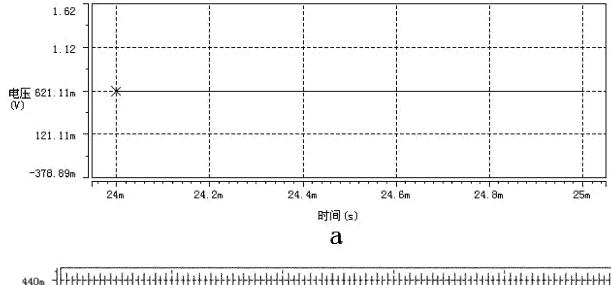

[0014] 图 7 是传统两级运算放大器电路和本发明运放电路的共模输入范围 ICMR 的仿真曲线对比图 (a 是传统两级运算放大器电路的共模输入范围 ICMR 的仿真曲线图, b 是本发明运放电路的共模输入范围 ICMR 的仿真曲线图):

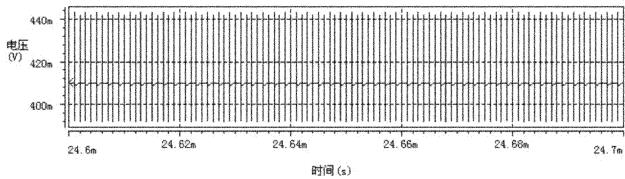

[0015] 图 8 是传统两级运算放大器电路和本发明运放电路失调电压的仿真曲线对比图;(a 是传统两级运算放大器电路的失调电压的仿真曲线图, b 是本发明运放电路失调电压的仿真曲线图)。

[0016] 图中,1. 交换控制电路,2. 第一级差分放大电路,3. 第二级共源放大电路,4. 补偿网络,m1. 第一 NMOS 管,m2. 第二 NMOS 管,m3. 第一 PMOS 管,m4. 第二 PMOS 管,m5. 第三 NMOS 管,m6. 第七 PMOS 管,m7. 第四 NMOS 管,m8. 第五 NMOS 管,m9. 第三 PMOS 管,m10. 第四 PMOS 管,m11. 第五 PMOS 管,m12. 第六 PMOS 管,m13. 第七 PMOS 管,m14. 第八 PMOS 管,m15. 第九 PMOS 管,m16. 第十 PMOS 管,R<sub>2</sub>. 消零电阻,C<sub>3</sub>. 补偿电容,C1. 电容;

#### 具体实施方式

[0017] 下面结合附图和具体实施方式对本发明进行详细说明。

如图 1 所示,传统的两级运算放大器电路包括第一级普通差分放大电路、第二级 [0018] 共源放大电路和补偿网络;第一级普通差分放大电路由第一NMOS管m1、第二NMOS管m2、第 三 NMOS 管 m5 和第一 PMOS 管 m3、第二 PMOS 管 m4 组成,第二级共源放大电路由第四 NMOS 管 m7 和第七 PMOS 管 m6 组成,补偿网络包括串联的消零电阻  $R_z$  和补偿电容  $C_c$ 。除此之外,参 考电流源  $I_{ref}$  和第五 NMOS 管 m8 为第三 NMOS 管 m5 和第四 NMOS 管 m7 提供镜像电流。其中, 第一 PMOS 管 m3、第二 PMOS 管 m4 和第七 PMOS 管 m6 三者的源端相连接并接工作电压 VDD; 第一PMOS 管 m3 和第二PMOS 管 m4 的栅极连接;第一PMOS 管 m3 的漏端与其栅极连接,还与 第一 NMOS 管 m1 的源端连接;第二 PMOS 管 m4 的漏端分别与第二 NMOS 管 m2 的源端、第七 PMOS 管 m6 的栅极和消零电阻 R<sub>2</sub> 的一端连接,消零电阻 R<sub>2</sub> 的另一端通过补偿电容 C<sub>2</sub> 输出 电压 OUT,补偿网络还通过电容 C1 接地;第七 PMOS 管 m6 的漏端与第四 NMOS 管 m7 的源端 连接;第一 NMOS 管 m1 和第二 NMOS 管 m2 的栅极分别接集成运放的输入信号 in1 和 in2,第 一 NMOS 管 m1 和第二 NMOS 管 m2 的漏端连接并同时接第三 NMOS 管 m5 的源端 ;第三 NMOS 管 m5、第五 NMOS 管 m8 和第四 NMOS 管 m7 的栅极连接,第三 NMOS 管 m5、第五 NMOS 管 m8 和第四 NMOS 管 m7 的漏端连接并接地;第五 NMOS 管 m8 的源端与栅极连接,并接工作电压 VDD。第 一级普通差分放大电路将差模输入电压转换为差模电流,这个差模电流作用在由第一 PMOS 管 m3 和第二 PMOS 管 m4 组成的电流镜负载上恢复成放大的单端电压输出,第二级共源放大 电路中第七 PMOS 管 m6 为共源接法,第四 NMOS 管 m7 作为负载管,构成输出级放大电路,输 出电压 OUT,补偿网络起到频率补偿的作用。在传统的两级运算放大电路中往往由于工艺偏 差等原因导致两个差分输入管特性存在不对称现象,这会使得在输入信号为0时,输出仍 然存在输出,带来运算放大器的输入失调电压。

[0019] 如图 2 所示,本发明公开了一种减小两级运算放大器输入失调电压的电路结构,包括交换控制电路 1、带输出交换功能的第一级差分放大电路 2、第二级共源放大电路 3 以及补偿网络 4;交换控制电路 1 的输出端与第一级差分放大电路 2 的输入端连接,第一级差分放大电路 2 的输出端与第二级共源放大电路 3 的输入端连接,第二级共源放大电路 3 的输入端与输出端之间还连接有补偿网络 4。交换控制电路 1 的输入信号连接集成运放的输入信号 in1 和 in2,整个集成运放的输入信号 in1 和 in2 不是直接连接第一级差分放大电路 2 的输入,而是作为交换控制电路 1 的输入信号 :交换控制电路 1 的输出信号 ea1 和 ea2 作为第一级差分放大电路 2 的输入,第一级差分放大电路 2 的输出信号 out\*连接第二级共源放大电路 3 的输入,第二级共源放大电路 3 的输入,第二级共源放大电路 3 的输入之间接入补偿网络 4。

[0020] 集成运放的失调电压主要是由于工艺偏差使得差分输入级电路很难做到完全对称引起的,本发明采用控制信号交换差分放大器的两个输入端来消除差分输入端不对称引起的失调,为了不改变运放的输出电压和输入电压的相位关系,同时在差分放大器的输出端也通过控制信号进行相应的交换。

[0021] 如图 3 所示,本发明交换控制电路 1 主要由 4 个 PMOS 管组成,分别为:第七 PMOS 管 m13、第八 PMOS 管 m14、第九 PMOS 管 m15 和第十 PMOS 管 m16;第七 PMOS 管 m13 和第八 PMOS 管 m14 的源端接输入信号 in1,第九 PMOS 管 m15 和第十 PMOS 管 m16 的源端接输入信号 in2;第八 PMOS 管 m14 和第九 PMOS 管 m15 的栅极分别接控制信号 ck1,第七 PMOS 管 m13 和第十 PMOS 管 m16 的栅极分别接控制信号 ck2;第八 PMOS 管 m14 和第十 PMOS 管 m16 的漏端相连

接,其输出信号为 ea1;第七 PMOS 管 m13 和第九 PMOS 管 m15 的漏端相连接,其输出信号为 ea2。控制信号 ck1 和控制信号 ck2 为两个相位相反的占空比为 50%的某一频率的控制信号。当 ck1 为高电平,ck2 为低电平时,输入信号 in1 通过第七 PMOS 管 m13 连接到 ea2, in2 通过第十 PMOS 管 m16 连接到 ea1;当 ck1 为低电平,ck2 为高电平时,输入信号 in1 通过第八 PMOS 管 m14 连接到 ea1, in2 通过第九 PMOS 管 m15 连接到 ea2。可见,通过 ck1 和 ck2 的控制,可以实现输入端信号 in1 和 in2 的交换。

[0022] 本发明中的第一级差分放大电路 2、第二级源极放大电路 3 以及补偿网络 4 如图 4 所示,第一级差分放大电路 2 在传统的单端输出差分放大器的基础上增加了由 ck1 和 ck2 控制的 4 个 PMOS 管 m9 ~ m12,其作用是根据交换控制电路 1 中输入信号的输入端不同选择差分放大器的输出 out1 或者 out2 作为第二级共源放大的输入信号 out\*,以保证差分运放的输出电压与输入电压之间的相位关系固定。

其具体结构为:第一级差分放大电路2包括第一NMOS管m1、第二NMOS管m2、第三 NMOS 管 m5、第四 NMOS 管 m7、第五 NMOS 管 m8、第一 PMOS 管 m3、第二 PMOS 管 m4、第三 PMOS 管 m9、第四 PMOS 管 m10、第五 PMOS 管 m11 和第六 PMOS 管 m12;第二级共源放大电路 3 包括 第七 PMOS 管 m6;补偿网络 4 包括串联的消零电阻  $R_z$  和补偿电容  $C_c$ 。第一 PMOS 管 m3、第二 PMOS 管 m4 和第七 PMOS 管 m6 三者的源端相连接并接工作电压 VDD;第一 PMOS 管 m3 和第二 PMOS 管 m4 的栅极连接;第一 PMOS 管 m3 的漏端经过输出端 out1 与第一 NMOS 管 m1 的源端 连接,第二 PMOS 管 m4 的漏端经过输出端 out2 与第二 NMOS 管 m2 的源端连接;第一 NMOS 管 m1 和第二 NMOS 管 m2 的栅极分别接信号 ea1 和信号 ea2,第一 NMOS 管 m1 和第二 NMOS 管 m2 的漏端连接并同时接第三 NMOS 管 m5 的源端;第三 NMOS 管 m5、第五 NMOS 管 m8 和第四 NMOS 管 m7 的栅极连接,第三 NMOS 管 m5、第五 NMOS 管 m8 和第四 NMOS 管 m7 的漏端连接并接地; 第五 NMOS 管 m8 的源端与栅极连接,并接工作电压 VDD;第三 PMOS 管 m9 和第四 PMOS 管 m10 的源端分别接第一 PMOS 管 m3 与第二 PMOS 管 m4 的栅极,第三 PMOS 管 m9 和第四 PMOS 管 m10的栅极分别接控制信号ck2和控制信号ck1,其漏端分别接输出端out1和输出端out2; 第五 PMOS 管 m11 和第六 PMOS 管 m12 的源端分别接输出端 out1 和输出端 out2,其栅极分别 接控制信号 ck1 和控制信号 ck2,第五 PMOS 管 m11 和第六 PMOS 管 m12 的漏端相连接并接输 出端 out\*;输出端 out\*分别与消零电阻 R<sub>2</sub>的一端和第七 PMOS 管 m6 的栅极连接;第七 PMOS 管 m6 的漏端与第四 NMOS 管 m7 的源端连接;消零电阻 R2 的另一端通过补偿电容 C2 输出电 压 OUT,补偿网络 4 还通过电容 C1 接地。

[0024] 当 ck1 为高电平, ck2 为低电平时, 第三 PMOS 管 m9 和第六 PMOS 管 m12 导通, 第四 PMOS 管 m10 和第五 PMOS 管 m11 截止, 第三 PMOS 管 m9 的导通使得第二 PMOS 管 m4 和第一 PMOS 管 m3 构成镜像电流源作为差分放大器的负载, 第二 PMOS 管 m4 复制第一 PMOS 管 m3 的电流, 第六 PMOS 管 m12 的导通使得 out 2 端接通输出端 out\*; 当 ck1 为低电平, ck2 为高电平时, 第四 PMOS 管 m10 和第五 PMOS 管 m11 导通, 第三 PMOS 管 m9 和第六 PMOS 管 m12 截止, 第四 PMOS 管 m10 的导通使得第一 PMOS 管 m3 和第二 PMOS 管 m4 构成镜像电流源作为差分放大器的负载, 第一 PMOS 管 m3 复制第二 PMOS 管 m4 的电流, 第五 PMOS 管 m11 的导通使得 out 1 端接通输出端 out\*。out\*端后面连接的是第二级共源放大电路 3 (第七 PMOS 管 m6) 以及补偿网络 4。

[0025] 整个减小两级运算放大器输入失调电压电路结构的工作原理是:当 ck1 为高电

平, ck2 为低电平时,第三 PMOS 管 m9、第六 PMOS 管 m12、第七 PMOS 管 m13 和第十 PMOS 管 m16 导通,第四 PMOS 管 m10、第五 PMOS 管 m11,第八 PMOS 管 m14 和第九 PMOS 管 m15 截止,差分输入的正端 ea2 的值为输入信号 in1, ea1 的值为 in2,差分的输出节点为 out2。反之,当 ck1 为低电平, ck2 为高电平时,第三 PMOS 管 m9、第六 PMOS 管 m12、第七 PMOS 管 m13 和第十 PMOS 管 m16 截止,第四 PMOS 管 m10、第五 PMOS 管 m11,第八 PMOS 管 m14 和第九 PMOS 管 m15 导通,差分输入的正端 ea2 的值为输入信号 in2, ea1 的值为 in1,差分的输出节点为 out1。 [0026] 采用 HSPICE 基于 0.5 m 混合信号模型对电路进行仿真,如图 5 所示,是传统两级运放电路和本发明两级运放电路的开环频率响应,由 a 图可以看出,传统两级运放电路的增益为 84dB,相位裕度为 76°;由 b 图可以看出,本发明运放电路的增益为 84dB,相位裕度为 60°;说明本发明运放电路的稳定性更好。

[0027] 如图 6 所示,是传统两级运放电路和本发明两级运放电路的电源电压抑制比的仿真曲线,由 a 图可以看出,传统两级运放电路的 PSRR 为 89. 2dB,由 b 图可以看出,本发明运放电路的 PSRR 为 90. 88dB,说明本发明运放电路的电源抑制比略有提高,电源电压波动时对输出电压的影响很小。

[0028] 如图 7 所示,是传统两级运放电路和本发明两级运放电路的共模输入范围 (ICMR) 的仿真曲线,由 a 图可以看出,传统两级运放电路的 ICMR 为 1.3 ~ 2.9V;由 b 图可以看出,本发明运放电路的 ICMR 为 1.2 ~ 2.9V。说明与传统两级运放电路相比,本发明运放电路的最小共模输入电压减小了,即增大了共模输入范围。

[0029] 图 8 是传统两级运放电路和本发明两级运放电路的输入失调电压  $V_{os}$  的仿真曲线,其值是通过设置差动输入为零来测量的。由 a 图可以看出,传统两级运放电路的  $V_{os}$  为 621. 11mV;由 b 图可以看出,本发明运放电路的  $V_{os}$  约为 417mV,图中的尖峰是由于开关的切换产生的。说明采用本发明的运放的输入失调电压减小了 204mV。

图 1

图 2

图 4

$\mathbf{a}$

b

图 5

图 6

图 7

b

图 8