# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 102177549 B (45) 授权公告日 2014.03.19

(21)申请号 200980140302.6

(22) 申请日 2009.10.14

(30) 优先权数据

61/105, 061 2008. 10. 14 US 61/111,013 2008.11.04 US 12/401, 963 2009. 03. 11 US

(85) PCT国际申请进入国家阶段日 2011. 04. 11

(86) PCT国际申请的申请数据 PCT/CA2009/001451 2009. 10. 14

(87) PCT国际申请的公布数据 W02010/043032 EN 2010.04.22

(73)专利权人 莫塞德技术公司 地址 加拿大安大略省

(72) 发明人 金镇祺 潘弘柏

(74) 专利代理机构 北京泛华伟业知识产权代理 有限公司 11280

代理人 王勇

(51) Int. CI.

*G11C* 7/10(2006.01) G11C 16/06 (2006.01) *G11C* 5/06 (2006, 01) G11C 7/22 (2006, 01)

(56) 对比文件

CN 1437718 A, 2003. 08. 20, 全文.

CN 1692343 A, 2005.11.02, 全文.

CN 101278354 A, 2008. 10. 01, 全文.

US 2008/0123423 A1, 2008. 05. 29, 说明书第 [0068] 段至第 [0079] 段,附图 5.

US 2004/0186948 A1, 2004. 09. 23, 全文.

US 2007/0263425 A1, 2007.11.15, 说明书第 [0015] 段至第 [0039] 段, 附图 1,2.

审查员 白桦

权利要求书4页 说明书22页 附图14页

## (54) 发明名称

具有用于将分立存储装置与系统相连接的桥 接装置的复合存储器

#### (57) 摘要

一种复合存储装置,它包括分立的存储装置 和用于控制这些分立存储装置的桥接装置,该桥 接装置响应于全局存储器控制信号来控制这些分 立存储装置,全局存储器控制信号具有与这些存 储装置不兼容的格式或协议。这些分立存储装置 可以是能用商业手段得到的成品存储装置或者定 制存储装置,它们对本机或本地存储器控制信号 m 做出响应。全局和本地存储器控制信号包括各自 具有不同格式的命令和命令信号。该复合存储装 置包括系统级封装,该系统级封装包括分立存储 装置和桥接装置的半导体管芯,或者该复合存储 装置可以包括安装有封装分立存储装置和封装桥 接装置的印刷电路板。

1. 一种复合存储装置封装,包括:

至少一个分立存储装置,用于响应于具有第一格式的本地存储器控制信号执行存储器操作;和

桥接装置,用于接收具有第二格式的全局存储器控制信号并且用于将该全局存储器控制信号转换为本地存储器控制信号,该桥接装置和至少一个分立存储装置彼此之间以堆叠方式放置,并且

桥接装置包括:

存储装置接口,该存储装置接口具有与所述至少一个分立存储装置相连接的本地输入/输出端口;和

桥接装置输入/输出接口,桥接装置输入/输出接口具有:

接收全局存储器控制信号的全局输入端口,和

全局输出端口,用于输出下列中的一个:i)全局存储器控制信号;ii)来自所述至少一个分立存储装置的读出数据,并且

全局输入端口和全局输出端口中的至少一个被配置为耦合至另一桥接装置。

- 2. 按照权利要求 1 所述的复合存储装置封装,其中桥接装置被堆叠在所述至少一个分立存储装置顶部。

- 3. 按照权利要求 1 所述的复合存储装置封装,其中复合存储装置封装包括多个分立存储装置,多个分立存储装置中的各个分立存储装置以错开的阶梯样式彼此堆叠起来,以露出所述多个分立存储装置中每一个的焊盘。

- 4. 按照权利要求 3 所述的复合存储装置封装,其中多个分立存储装置中的各个分立存储装置的焊盘面朝相对于复合存储装置封装的基板的向上方向。

- 5. 按照权利要求 1 所述的复合存储装置封装,其中全局通信端子将桥接装置输入 / 输出接口的全局输入端口和全局输出端口电耦合到复合存储装置封装的引线上。

- 6. 按照权利要求 1 所述的复合存储装置封装,其中全局通信端子将桥接装置输入 / 输出接口的全局输入端口和全局输出端口无线耦合到复合存储装置封装的引线上。

- 7. 按照权利要求 1 所述的复合存储装置封装,其中全局存储器控制信号是在全局命令中接收的,全局命令还包括地址报头。

- 8. 按照权利要求 1 所述的复合存储装置封装,其中第一格式包括串行数据接口格式, 第二格式包括异步闪速存储器格式。

- 9. 按照权利要求 1 所述的复合存储装置封装,其中第一格式包括 0NFi 规范接口格式, 第二格式包括异步闪速存储器格式。

- 10. 按照权利要求 3 所述的复合存储装置封装,其中多个分立存储装置具有相同的类型。

- 11. 按照权利要求 3 所述的复合存储装置封装,其中多个分立存储装置具有不同的类型。

- 12. 按照权利要求 3 所述的复合存储装置封装,其中多个分立存储装置是异步 NAND 闪速存储装置。

- 13. 一种复合存储装置封装,包括:

至少一个分立存储装置,用于响应于具有第一格式的本地存储器控制信号执行存储器

### 操作;和

桥接装置,用于接收具有第二格式的全局存储器控制信号并且用于将该全局存储器控制信号转换为本地存储器控制信号,该桥接装置和至少一个分立存储装置彼此之间以堆叠方式放置,并且其中该桥接装置包括:

存储装置接口,该存储装置接口具有与所述至少一个分立存储装置相连接的本地输入/输出端口;和,

桥接装置输入/输出接口,具有:

接收全局存储器控制信号的全局输入端口,和

全局输出端口,用于提供全局存储器控制信号和来自所述至少一个分立存储装置的读出数据之一。

- 14. 按照权利要求 13 所述的复合存储装置封装,其中本地通信端子将多个分立存储装置中的每一个的输入/输出端口电耦合到桥接装置的存储装置接口的本地输入/输出端口上。

- 15. 按照权利要求 13 所述的复合存储装置封装,其中本地通信端子的通道将来自存储装置接口的时钟端口的时钟信号和存储装置接口的多个并行数据输入/输出端口电耦合到多个分立存储装置之一。

- 16. 按照权利要求 15 所述的复合存储装置封装,其中本地通信端子的 i 个通道被电耦合到相应的 i 个分立存储装置,其中 i 是至少为 1 的整数值。

- 17. 按照权利要求 15 所述的复合存储装置封装,其中本地通信端子的通道被并行地电连接到多个分立存储装置中的每一个上。

- 18. 按照权利要求 17 所述的复合存储装置封装,其中该通道包括预先在复合存储装置封装的基板上形成的导电轨迹。

- 19. 按照权利要求 13 所述的复合存储装置封装,其中本地通信端子将多个分立存储装置中的每一个的输入/输出端口无线耦合到桥接装置的存储装置接口的本地输入/输出端口上。

- 20. 按照权利要求 13 所述的复合存储装置封装,其中全局通信端子将桥接装置输入/输出接口的全局输入端口和全局输出端口电耦合到复合存储装置封装的引线上。

- 21. 按照权利要求 13 所述的复合存储装置封装,其中全局通信端子将桥接装置输入/输出接口的全局输入端口和全局输出端口无线耦合到复合存储装置封装的引线上。

- 22. 按照权利要求13 所述的复合存储装置封装,其中本地输入/输出端口、全局输入端口和全局输出端口都与复合存储装置封装的引线电耦合。

- 23. 按照权利要求 13 所述的复合存储装置封装,其中全局存储器控制信号是在全局命令中接收的,全局命令还包括地址报头。

- 24. 按照权利要求 23 所述的复合存储装置封装,其中地址报头包括全局装置地址和本地装置地址;全局装置地址与所选择的复合存储装置相对应;本地装置地址与所选择的复合存储装置中的至少一个分立存储装置中的选定分立存储装置相对应。

- 25. 按照权利要求 13 所述的复合存储装置封装,其中第一格式包括串行数据接口格式,第二格式包括异步闪速存储器格式。

- 26. 按照权利要求 13 所述的复合存储装置封装,其中第一格式包括 0NFi 规范接口格

式,第二格式包括异步闪速存储器格式。

27. 一种存储器模块,包括:

具有与印刷电路板的导电轨迹焊接的存储装置引线的至少一个封装分立存储装置,该至少一个封装分立存储装置用于响应于具有第一格式的本地存储器控制信号执行存储器操作;和

具有与印刷电路板的导电轨迹焊接的桥接装置引线的至少一个封装桥接装置,该至少一个封装桥接装置用于接收具有第二格式的全局存储器控制信号和用于将该全局存储器控制信号转换为本地存储器控制信号,并且

该至少一个封装桥接装置包括:

存储装置接口,该存储装置接口具有与至少一个封装分立存储装置相连接的本地输入/输出端口;和

桥接装置输入/输出接口,桥接装置输入/输出接口具有:

接收全局存储器控制信号的全局输入端口,和

全局输出端口,用于输出下列中的一个:i)全局存储器控制信号;ii)来自至少一个分立存储装置的读出数据,并且

全局输入端口和全局输出端口中的至少一个被配置为耦合至另一桥接装置。

- 28. 按照权利要求 27 所述的存储器模块,其中全局存储器控制信号是在全局命令中接收的,全局命令还包括地址报头。

- 29. 按照权利要求 27 所述的存储器模块,其中第一格式包括串行数据接口格式,第二格式包括异步闪速存储器格式。

- 30. 按照权利要求 27 所述的存储器模块,其中第一格式包括 0NFi 规范接口格式,第二格式包括异步闪速存储器格式。

- 31. 按照权利要求 27 所述的存储器模块,其中存储器模块包括多个封装分立存储装置并且多个封装存储装置的类型相同。

- 32. 按照权利要求 27 所述的存储器模块,其中存储器模块包括多个封装分立存储装置,并且多个封装存储装置具有不同的类型。

- 33. 按照权利要求 27 所述的存储器模块,其中存储器模块包括多个封装分立存储装置,并且多个封装存储装置是异步 NAND 闪速存储装置。

- 34. 一种存储器模块,包括:

具有与印刷电路板的导电轨迹焊接的存储装置引线的至少一个封装分立存储装置,该至少一个封装分立存储装置用于响应于具有第一格式的本地存储器控制信号执行存储器操作;和

具有与印刷电路板的导电轨迹焊接的桥接装置引线的至少一个封装桥接装置,该至少一个封装桥接装置用于接收具有第二格式的全局存储器控制信号和用于将该全局存储器控制信号转换为本地存储器控制信号,并且其中封装桥接装置包括:

存储装置接口,该存储装置接口具有与至少一个封装分立存储装置相连接的本地输入/输出端口;和,

桥接装置输入/输出接口,桥接装置输入/输出接口具有:

接收全局存储器控制信号的全局输入端口,和

全局输出端口,全局输出端口提供全局存储器控制信号和来自至少一个分立存储装置的读出数据之一。

- 35. 按照权利要求 34 所述的存储器模块,其中本地通信端子经由印刷电路板的预先形成的导电轨迹将至少一个封装分立存储装置的输入/输出端口电耦合到封装桥接装置的存储装置接口的本地输入/输出端口上。

- 36. 按照权利要求 34 所述的存储器模块,其中全局通信端子将桥接装置输入/输出接口的全局输入端口和全局输出端口电耦合到印刷电路板的预先形成的导电轨迹上。

- 37. 按照权利要求 34 所述的存储器模块,其中本地通信端子的通道将来自存储装置接口的时钟端口的时钟信号和存储装置接口的多个并行数据输入/输出端口电耦合到多个封装存储装置之一。

- 38. 按照权利要求 37 所述的存储器模块,其中本地通信端子的 i 个通道被电耦合到相应的 i 个封装存储装置,其中 i 是至少为 1 的整数值。

- 39. 按照权利要求 37 所述的存储器模块,其中本地通信端子的通道被并行地电连接到 多个封装存储装置中的每一个上。

- 40. 按照权利要求 39 所述的存储器模块,其中通道包括印刷电路板的导电轨迹。

- 41. 一种存储器模块,包括:

具有与印刷电路板的导电轨迹焊接的存储装置引线的至少一个封装分立存储装置,该至少一个封装分立存储装置用于响应于具有第一格式的本地存储器控制信号执行存储器操作;和

具有与印刷电路板的导电轨迹焊接的桥接装置引线的至少一个封装桥接装置,该至少一个封装桥接装置用于接收具有第二格式的全局存储器控制信号和用于将该全局存储器控制信号转换为本地存储器控制信号,并且

其中全局存储器控制信号是在全局命令中接收的,全局命令还包括地址报头,并且地址报头包括全局装置地址和本地装置地址;全局装置地址与所选择的复合存储装置相对应;本地装置地址与所选择的复合存储装置中的至少一个封装分立存储装置中的选定分立存储装置相对应。

# 具有用于将分立存储装置与系统相连接的桥接装置的复合 存储器

[0001] 相关申请的交叉引用

[0002] 本申请要求 2008 年 10 月 14 日提交的美国临时专利申请第 61/105061 号、2008 年 11 月 4 日提交的美国临时专利申请第 61/111013 号和 2009 年 3 月 11 日提交的美国专利申请第 12/401963 号的优先权益,这些在先申请的公开内容以引用的方式全部明确地并入本文。

# 技术领域

## 背景技术

[0003] 半导体存储装置是现有工业和消费电子产品中的重要部件。例如,计算机、移动电话和其它便携式电子设备全部依赖某种形式的存储器来存储数据。虽然很多存储装置一般情况下是能够以商品或者说分立存储装置的形式得到的,但是对更高集成度和更高输出(I/0)带宽的需求导致了可以与诸如微控制器和其它处理电路之类的系统集成在一起的嵌入式存储器的开发。

[0004] 大多数消费电子产品采用诸如闪速存储装置之类的非易失性装置来存储数据。对闪速存储装置的需求量不断明显加大,因为这些装置很适合于各种各样的需要很大的非易失性存储量而又占用很小物理区域的应用。例如,在各种各样的电子消费品中往往会发现闪存,比如数码相机、蜂窝电话、通用串行总线(USB)闪存驱动器和便携式音乐播放器,这些装置用闪存来存储数据。而且,闪存装置被用作替代硬盘驱动器(HDD)的固态驱动器(SSDs)。这些便携式装置最适于在形态因子尺寸和重量方面实现最小化。不幸的是,多媒体和SSD应用需要很大的存储量,这会增大它们产品的形态因子尺寸和重量。因此,消费者产品制造商通过限制产品中包含的物理存储量来达到折衷,以保持产品尺寸和重量能够得到消费者接受。此外,虽然闪速存储器的每单位面积密度比DRAM或SRAM要高,但是它的性能是有限的,因为它的 I/0 带宽相对较低,对它的读写吞吐量造成了负面影响。

[0005] 为了满足对存储装置应用日益增加的需求以及存储装置应用无处不在的现状,就希望提供高性能的存储装置,即,具有更高 I/0 带宽、更高读写吞吐量和更高操作灵活性的装置。

### 发明内容

[0006] 公开了一种包括桥接装置和分立存储装置的复合存储装置。这些装置是例如存储装置,比如闪速存储器、动态随机存取装置(DRAM)、静态随机存取装置(SRAM)、DiNOR 闪速 EEPROM 装置、串联闪速 EEPROM 装置、铁 RAM 装置、磁 RAM 装置、相变 RAM 装置或者这些和/或其它装置的任何适当组合。

[0007] 在一个方面,给出了包括至少一个分立存储装置和桥接装置的复合存储装置。该至少一个分立存储装置响应于具有第一格式的本地存储器控制信号执行存储器操作。桥接

装置接收具有第二格式的全局存储器控制信号并且将该全局存储器控制信号转换成本地 存储器控制信号。

[0008] 在一种实施方式中,桥接装置可以包括与至少一个分立存储装置连接的本地输入/输出端口,接收全局存储器控制信号的全局输入端口,和提供全局存储器控制信号和来自至少一个分立存储装置的读出数据之一的全局输出端口。

[0009] 所述至少一个分立存储装置和该桥接装置可以封装在一起。全局输入端口和全局输出端口可以与封装的引线电耦合。可以使用导电体将本地输入/输出端口耦合到所述至少一个分立存储装置。按照另外一种可选方案,本地输入/输出端口可以被无线耦合到所述至少一个分立存储装置。

[0010] 在另一种实施方式中,至少一个分立存储装置可以是封装存储装置,桥接装置可以是封装桥接装置。封装存储装置和封装桥接装置可以被安装在印刷电路板上。本地输入/输出端口、全局输入端口和全局输出端口可以都与封装桥接装置的引线电耦合。封装存储装置可以具有与封装桥接装置的本地输入/输出端口电连接的存储器引线。

[0011] 在一种实施方式中,复合存储装置中的全局存储器控制信号可以在全局命令中接收。全局命令可以此外还包括地址报头。地址报头可以包括与所选择的复合存储装置相对应的全局装置地址和与所选择的复合存储装置中的至少一个封装分立存储装置中的选定分立存储装置相对应的本地装置地址。

[0012] 在复合存储装置的一种实施方式中,第一格式可以包括串行数据接口格式或 0NFi 规范接口格式,第二格式可以包括异步闪速存储器格式。

[0013] 在另一个方面,给出了一种存储系统,它包括存储器控制器和 n 个复合存储装置,这 n 个复合存储装置彼此之间以及与存储器控制器之间串联连接,形成环形拓扑结构构造。存储器控制器提供与存储器操作相应的全局命令。n 个复合存储装置中的各个复合存储装置具有 m 个分立存储装置和一个桥接装置。n 个复合存储装置中的选定复合存储装置的桥接装置接收全局命令,以便向 m 个分立存储装置中的选定分立存储装置提供与存储器操作相对应的本地存储器控制信号,其中 n 和 m 是大于 0 的整数值。

[0014] 在一种实施方式中,n个复合存储装置中的各个复合存储装置可以是系统级封装(SIP)或印刷电路板(PCB)。m个分立存储装置和桥接装置可以是具有与PCB中的导电轨迹相接的封装引线的封装装置。

[0015] 在另一种实施方式中,桥接装置可以包括桥接装置输入/输出接口、格式转换电路和存储装置接口。桥接装置输入/输出接口具有用于输入全局命令的输入端口和用于提供全局命令的输出端口。桥接装置将全局装置地址与全局装置地址寄存器中存储的预定地址相比较,并且在全局装置地址与该预定地址匹配的时候,格式转换电路将全局命令的全局存储器控制信号从第一格式转换为具有第二格式的本地存储器控制信号。存储装置接口然后响应于本地装置地址将本地存储器控制信号提供给选定的分立存储装置。

[0016] 在一种实施方式中,格式转换电路包括命令格式转换器和数据格式转换器。命令格式转换器将第一格式的全局存储器控制信号转换为具有第二格式的本地存储器控制信号。数据格式转换器将来自选定分立存储装置的读出数据从第二格式转换为第一格式。在写入操作中,数据格式转换器将写入数据从第一格式转换为第二格式。

[0017] 在再另一种实施方式中,存储系统中的复合存储装置可以具有不同类型的分立存

储装置。在这些情况下,桥接装置可以包括与各个不同类型的分立存储装置相对应的多个 格式转换电路。

[0018] 按照另一个方面,给出了一种复合存储装置封装。该复合存储装置封装包括至少一个分立存储装置和一个桥接装置。该至少一个分立存储装置响应于具有第一格式的本地存储器控制信号执行存储器操作。桥接装置接收具有第二格式的全局存储器控制信号并且将该全局存储器控制信号转换成本地存储器控制信号。桥接装置和至少一个分立存储装置是彼此之间以堆叠方式放置的。

[0019] 在再另一个方面,给出了一种存储器模块。该存储器模块包括至少一个封装分立存储装置和一个封装桥接装置。该至少一个封装分立存储装置具有与印刷电路板的导电轨迹焊接的存储装置引线。该至少一个封装存储装置响应于具有第一格式的本地存储器控制信号执行存储器操作。该封装桥接装置具有与印刷电路板的导电轨迹焊接的桥接装置引线。至少一个封装桥接装置接收具有第二格式的全局存储器控制信号并且将该全局存储器控制信号转换成本地存储器控制信号。

[0020] 在此外的一个方面,给出了一种响应于具有全局格式的全局信号访问分立存储装置的桥接装置。该桥接装置包括桥接装置输入/输出接口和桥接装置存储装置接口。该桥接装置输入/输出接口向和从桥接装置传送具有全局格式的全局信号。桥接装置存储装置接口在桥接装置和分立存储装置之间传送具有本地格式的本地信号。本地信号在功能上与全局信号相当并且具有不同于全局格式的本地格式。

[0021] 在另一个方面,给出了具有存储器控制器和 n 个复合存储装置的存储系统。存储器控制器提供与存储器操作相应的全局命令。n 个复合存储装置彼此之间以及与存储器控制器之间并联连接,其中 n 个复合存储装置中的各个复合存储装置具有 m 个分立存储装置和一个桥接装置。n 个复合存储装置中的选定复合存储装置的桥接装置接收全局命令,以便向 m 个分立存储装置中的选定分立存储装置提供与存储器操作相对应的本地存储器控制信号,其中 n 和 m 是大于 0 的整数值。

[0022] 在结合附图阅读了下面本发明具体实施方式的介绍之后,本发明的其它方面和特征对于本领域的普通技术人员将会变得显而易见。

#### 附图说明

[0023] 现在将参照附图仅以举例的方式介绍本发明的实施方式,其中:

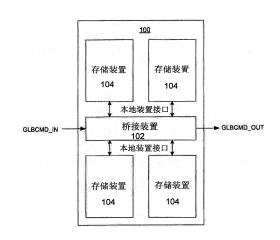

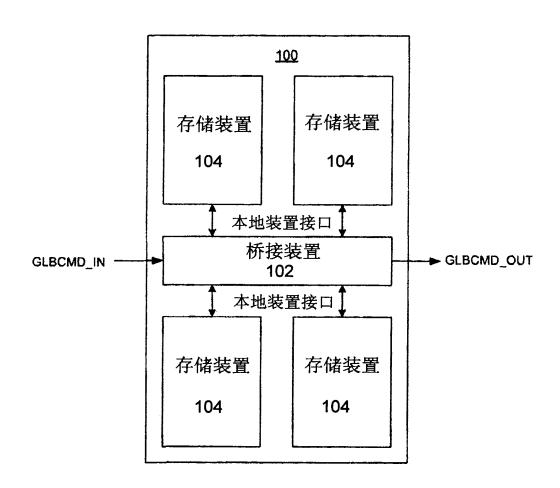

[0024] 附图 1A 是实例非易失性存储系统的框图;

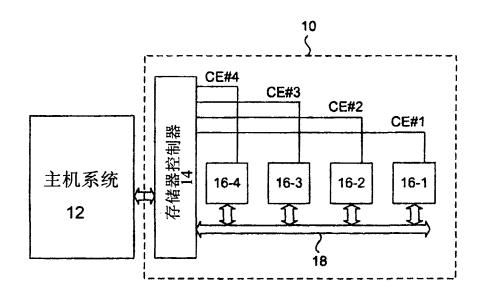

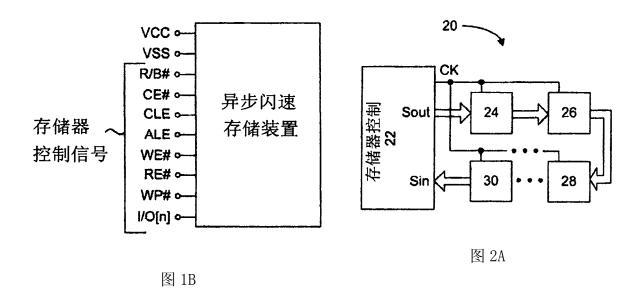

[0025] 附图 1B 是附图 1A 的实例存储系统中使用的分立闪速存储装置的示意图;

[0026] 附图 2A 是实例串行存储器系统的框图;

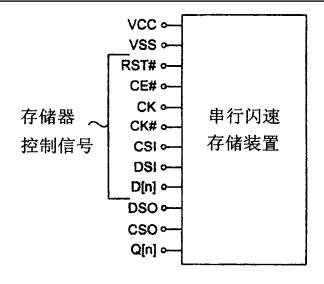

[0027] 附图 2B 是附图 2A 的实例存储系统中使用的分立串行接口闪速存储装置的示意图;

[0028] 附图 3A 是按照一种实施方式的具有四个分立存储装置和一个桥接装置的复合存储装置的框图;

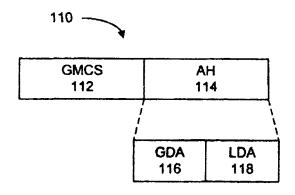

[0029] 附图 3B 是按照本发明实施方式的全局命令的图解说明;

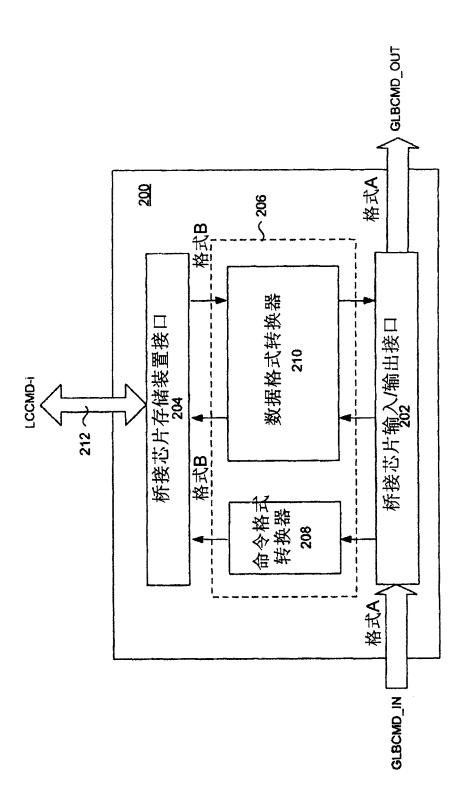

[0030] 附图 4 是按照一种实施方式的桥接装置的框图;

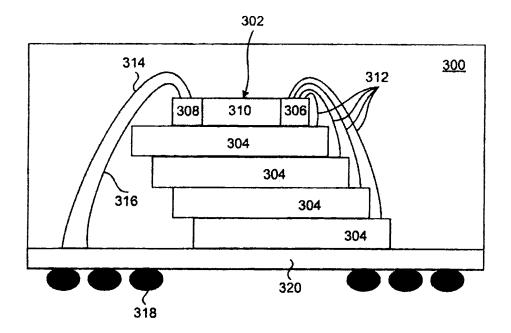

[0031] 附图 5A 是按照另一种实施方式的封装中复合存储装置的横截面图;

[0032] 附图 5 是按照另一种实施方式的封装中另一种可供选用的复合存储装置的横截面图:

[0033] 附图 6 是按照另一种实施方式的模块中具有与桥接装置相连的多个分立存储装置的存储系统的框图:

[0034] 附图 7 是按照一种实施方式的串联互接存储系统中具有与控制器相连的多个复合存储装置的存储系统的框图;

[0035] 附图 8 是表示按照本发明的实施方式的附图 3A 的桥接装置到 NAND 闪速存储装置的存储映像的框图:

[0036] 附图 9A、9B 和 9C 图解说明使用附图 3A 的桥接装置从一个 NAND 闪速存储装置中进行的实例读出操作;

[0037] 附图 10A、10B、10C 和 10D 图解说明针对附图 3A 的桥接装置的各个存储器区块的实例虚拟页配置:

[0038] 附图 11 是图解说明按照本发明实施方式的从复合存储装置中读取数据的方法的 流程图:和

[0039] 附图 12 是图解说明按照本发明实施方式的向复合存储装置写入数据的方法的流程图。

# 具体实施方式

[0040] 总的来说,本发明的实施方式涉及一种复合存储装置,它包括分立的存储装置和用于控制这些分立存储装置的桥接装置,该桥接装置响应于全局存储器控制信号来控制这些分立存储装置,全局存储器控制信号具有与这些存储装置不兼容的格式或协议。这些分立存储装置可以是能用商业手段得到的成品存储装置或者定制存储装置,它们对本机或本地存储器控制信号做出响应。全局和本地存储器控制信号包括各自具有不同格式的命令和命令信号。

[0041] 按照一种实施方式,桥接装置,或者芯片,包括桥接装置输入/输出接口;格式转换电路;和存储装置接口。桥接装置输入/输出接口以全局格式与存储器控制器或其它复合存储装置通信。格式转换电路将全局存储器控制信号从全局格式转换为与它所连接的分立存储装置相兼容的对应本地格式。全局格式仅由桥接装置接收到的全局存储器控制信号采用,而本地格式仅由分立存储装置使用的本地存储器控制信号采用。故而,存储装置接口以本地格式与桥接装置所连接的各个分立存储装置进行通信。

[0042] 按照本文所介绍技术的系统和装置可应用于具有多个串联连接装置的存储系统。这些装置可以是存储装置,比如动态随机存取存储器 (DRAM)、静态随机存取存储器 (SRAM)、闪速存储器、DiNOR 闪速 EEPROM 存储器、串联闪速 EEPROM 存储器、铁 RAM 存储器、磁 RAM 存储器、相变 RAM 存储器和任何其它适当类型的存储器。

[0043] 下面介绍两种不同的存储装置和系统,以帮助更深入地理解后面介绍的复合存储装置和桥接装置的实施方式。

[0044] 附图 1A 是与主机系统 12 集成在一起的非易失性存储系统 10 的框图。系统 10 包括与主机系统 12 通信的存储器控制器 14,以及多个非易失性存储装置 16-1、16-2、16-3 和 16-4。例如,非易失性存储装置 16-1-16-4 可以是分立的异步闪速存储装置。主机系统 12

包括诸如微控制器、微处理器或计算机系统之类的处理装置。附图 1A 的系统 10 被组织成包括一个通道 18,和并联地与通道 18 连接的存储装置 16-1-16-4。本领域技术人员应当理解,系统 10 可以有多于或少于四个存储装置与其相连。在目前所示的例子中,存储装置 16-1-16-4 是异步的并且是彼此并联连接的。

[0045] 通道 18 包括一组公共总线,这些公共总线包括与所有它的相应存储装置相连的数据和控制线。各个存储装置由存储器控制器 14 提供的芯片选择(使能)信号 CE1#, CE2#, CE3#和 CE4# 启用或禁用。在这个和后面的例子中,"#"都表示该信号是一个有效低逻辑电平信号。在这个方案中,一般情况下一次选择一个芯片选择信号,以启用非易失性存储装置 16-1-16-4 中相应的一个。存储器控制器 14 负责响应于主机系统 12 的操作,经由通道 18 向所选择的存储装置发出命令和数据。从存储装置输出的读出数据经由通道 18 被传送回到存储器控制器 14 和主机系统 12。可以认为系统 10 总体上包括多支路总线,在该多支路总线中,存储装置 16-1-16-4 相对于通道 18 而言并联连接。

[0046] 附图 1B 是分立闪速存储装置 16-1-16-4 之一的示意图,其可以用在附图 1A 的存储系统中。这个闪速存储装置包括数个输入输出端口,这些端口包括例如电源、控制端口和数据端口。术语"端口"指的是统称的存储装置内的输入或输出端子,包括例如封装引脚、封装焊剂凸块、芯片接线焊点和无线发射器和接收器。电源端口包括用于向闪速存储装置的所有电路供电的 VCC 和 VSS。可以提供额外的电源端口,仅仅为输入和输出缓冲器供电,这在本领域中是公知的。表 1 下面给出了控制和数据端口的列表,它们的相应描述、定义和实例逻辑状态。要注意的是,封装引脚和球栅阵列是用于将封装装置的信号或电压接到主板上的端口的物理实例。这些端口可以其它类型的连接,比如,用于内置和系统级封装(SIP)系统的端子和触点。

[0047] 表 1

[0048]

| 端口     | 描述                                    |  |  |

|--------|---------------------------------------|--|--|

| R/B#   | 就绪/忙: R/B#是开漏端口(open drain port),并且输出 |  |  |

|        | 信号用于表示装置的操作状态。R/B#信号在编程               |  |  |

|        | (program)、擦除和读取操作期间处于忙状态              |  |  |

|        | (R/B#=LOW),在操作完成之后返回到就绪状态             |  |  |

|        | (R/B#=HIGH).                          |  |  |

| CE#    | 芯片使能:在装置处于就绪状态期间,当CE#变为HIGH           |  |  |

|        | 时,装置进入低功率待机模式。当装置处于忙状态                |  |  |

|        | (R/B#=LOW)时,比如在编程或擦除或读取操作期间,          |  |  |

|        | CE#信号被忽略,并且即使CE#输入变为HIGH也不会进          |  |  |

|        | 入待机模式                                 |  |  |

| CLE    | 命令锁存使能: CLE输入信号用于控制操作模式命令向            |  |  |

|        | 内部命令寄存器内的装载。在CLE为HIGH的时候,在            |  |  |

|        | WE#信号的升边沿上,将来自I/O端口的命令锁存到命令           |  |  |

|        | 寄存器中。                                 |  |  |

| ALE    | 地址锁存使能(ALE): ALE信号用于控制地址信息向           |  |  |

|        | 内部地址寄存器内的装载。在ALE为HIGH时,在WE#           |  |  |

|        | 信号的升边沿上,将来自I/O端口的地址信息锁存到地址            |  |  |

|        | 寄存器中。                                 |  |  |

| WE#    | 写入使能:WE#信号用于控制从I/O端口的数据获取。            |  |  |

| RE#    | 读取使能: RE信号控制串行数据输出。数据在RE#的降           |  |  |

|        | 边沿之后可用。                               |  |  |

| WP#    | 写保护: WP#信号用于保护装置免遭意外编程或擦掉。            |  |  |

|        | 当WP#为LOW时,内部电压调节器(高压发生器)被重            |  |  |

|        | 置。这个信号通常用于在输入信号无效的时候上电/断电             |  |  |

|        | 期间保护数据。                               |  |  |

| I/O[n] | I/O端口:用作向/从装置传送地址、命令和输入/输出数           |  |  |

|        | 据的端口。变量n可以是任何非零整数值。                   |  |  |

[0050] 表 1 中给出的所有信号统称为针对附图 1B 中所示的实例闪速存储装置操作的存储器控制信号。要注意的是,最后一个端口 I/0[n] 被当做存储器控制信号,是因为它能够接收指示闪速存储装置执行具体操作的命令。因为端口 I/0[n] 上确立的命令是加在构成 I/0[n] 的各条专用线路上的逻辑状态的组合,所以 I/0[n] 的各个信号的逻辑状态按照与其它存储器控制信号之一相同的方式起作用。主要区别是,它是由 I/0[n] 逻辑状态的特定组合来控制闪速存储装置执行功能。命令是通过它的 I/0 端口接收的,并且命令信号包括

剩余的控制端口。本领域的技术人员知道,在命令中会提供用于执行具体存储器操作的操作码(op码)。除了芯片启用CE#之外,所有其它端口都与构成通道18的各条全局线路相接。由存储器控制器14向各个闪速存储装置提供各自的芯片启用信号。所有端口是以预定方式控制的,以执行存储器操作。这包括在I/0端口上提供地址、命令和I/0数据时的具体控制信号的信号定时和排序。因此,控制附图1B的异步闪速存储装置的存储器控制信号具有特定的格式或协议。

[0051] 附图 1A 的各个非易失性存储装置具有一个特定的数据接口,用于接收和提供数据。在附图 1A 的例子中,这是异步闪速存储装置中共用的并行数据接口。大家都知道,并行提供多个数据位的标准并行数据接口在工作在超出它们的整倍工作频率下工作时,易受大家所熟知的通信质量下降的影响,比如例如串扰、信号失真和信号衰减,这会降低信号质量。

[0052] 为了增加数据吞吐量,在共同拥有的名称为"Memory with Output Control"的美国专利公开第 20070153576 号中和共同拥有的名称为"Daisy Chain Cascading Devices"的美国专利公开第 20070076502 号中已经公开了具有串行数据接口的、以例如 200MHz 的频率串行接收和提供数据的存储装置。这被称为串行数据接口格式。如这些共同拥有的专利公开文本中所示,所介绍的存储装置可以被用在彼此串联连接的存储装置的系统中。

[0053] 附图 2A 是图解说明串行存储系统的原理特征的框图。在附图 2A 中,串联环形拓扑结构存储系统 20 包括具有一组输出端口 Sout 和一组输入端口 Sin 以及串联连接的存储装置 24、26、28 和 30。存储装置可以是例如串行接口闪速存储装置。虽然在附图 2A 中没有示出,但是各个存储装置具有一组输入端口 Sin 和一组输出端口 Sout。这些组输入和输出端口包括一个或多个将存储装置与其作为其中一部分的系统相接的独立输入/输出端口。在一个例子中,存储装置可以是闪速存储装置。作为替换方案,存储装置可以是 DRAM、SRAM、DiNOR 闪速 EEPROM、串行闪速 EEPROM、铁 RAM、磁 RAM 相变 RAM 或者任何其它合适类型的具有与特定命令结构兼容的、用于执行命令或用于将命令和数据传送到下一个存储装置的输入/输出接口的存储装置。目前附图 2A 的例子包括四个存储装置,但是替代结构可以包括单独一个存储装置或者任何适当数量的存储装置。由此,如果存储装置 24 因为与 Sout 相连而成为系统 20 的第一个装置,那么存储装置 30 就因为与 Sin 相连而成为第 N 个或最后一个装置,其中 N 是大于零的整数。于是存储装置 26 到 28 就是介于第一个和最后一个存储装置之间的串联连接的存储装置。在附图 2A 的例子中,存储装置 24 到 30 是同步的,并且彼此之间和与存储器控制器 22 之间串联连接。

[0054] 附图 2B 是可以用在附图 2A 的存储系统中的串行接口闪速存储装置(例如 24 到 30)的示意图。这个示例串行接口闪速存储装置包括电源端口、控制端口和数据端口。电源端口包括用于向闪速存储装置的所有电路供电的 VCC 和 VSS。可以提供额外的电源端口,仅仅为输入和输出缓冲器供电,这在本领域中是公知的。表 2 下面给出了控制和数据端口的列表、它们的相应描述和实例逻辑状态。

[0055] 表 2

[0056]

| 端口      | 描述                                   |  |  |  |

|---------|--------------------------------------|--|--|--|

| CK/ CK# | 时钟: CK是系统时钟输入。CK和CK#是差动时钟输入。所        |  |  |  |

|         | 有的命令、地址、输入数据和输出数据都要在两个方向上参           |  |  |  |

|         | 照CK和CK#的跨越边沿。                        |  |  |  |

| CE#     | 芯片使能: 当CE#为LOW时,装置被使能。一旦装置启动编        |  |  |  |

|         | 程或擦除操作,芯片使能端口可以被撤销。此外, CE# LOW       |  |  |  |

|         | 激活内部时钟信号,而CE# HIGH停用内部时钟信号。          |  |  |  |

| RST#    | 芯片复位: RST#提供对装置的复位。当RST#为HIGH时,装     |  |  |  |

|         | 置处于正常操作方式。当RST#为LOW时,装置将会进入复位        |  |  |  |

|         | 模式。                                  |  |  |  |

| D[n]    | 数据输入: (n=1,2,3,4,5,6,7或8)接收命令、地址和输入数 |  |  |  |

|         | 据。如果装置被配置为'1位链接模式(=缺省)',则D1是唯        |  |  |  |

|         | 一有效信号并且在CK/CK#的8个跨越内接收数据包的一个字        |  |  |  |

|         | 节。如果装置被配置为'2位链接模式',则D1和D2是仅有的有       |  |  |  |

|         | 效信号并且在CK/CK#的4个跨越内接收数据包的一个字节。        |  |  |  |

|         | 没有使用的输入端口接地。                         |  |  |  |

| Q[n]    | 数据输出: (n=1,2,3,4,5,6,7或8)在读取操作期间发送输出 |  |  |  |

|         | 数据。如果装置被配置为'1位链接模式(=缺省)',则Q1是        |  |  |  |

|         | 唯一有效信号并且在CK/CK#的8个跨越内发送数据包的一个        |  |  |  |

|         | 字节。如果装置被配置为'2位链接模式',则Q1和Q2是仅有的       |  |  |  |

|         | 有效信号并且在CK/CK#的4个跨越内发送数据包的一个字         |  |  |  |

|         | 节。没有使用的输出端口是DNC状态(=不连接)。             |  |  |  |

| CSI     | 命令选通输入:当CSI为HIGH时,通过D[n]的命令、地址和      |  |  |  |

|         | 输入数据在CK和CK#的跨越上被锁存。当CSI为LOW时,装       |  |  |  |

|         | 置忽视从D[n]输入的信号。                       |  |  |  |

| CSO     | 命令选通输出:回波信号CSO是源信号CSI的重新发送版本。        |  |  |  |

| DSI     | 数据选通输入:为HIGH时使能Q[n]缓存器。当DSI为LOW时,    |  |  |  |

|         | Q[n]缓冲器保存之前访问的数据。                    |  |  |  |

| DSO     | 数据选通输出:回波信号DSO是源信号DSI的重新发送版本。        |  |  |  |

[0058] 除了信号 CSO、DSO 和 Q[n] 之外,表 2 中给出的所有信号都是针对附图 2B 中所示的实例闪速存储装置的操作的存储器控制信号。CSO 和 DSO 是 CSI 和 DSI 的重新发送版本,并且 Q[n] 是用于提供命令和数据的输出。命令是通过它的 D[n] 端口接收的,并且命令信号包括控制端口 RST#、CE#、CK、CK#、CSI 和 DSI。在附图 2A 中所示的实例构造中,所有信号都是从存储器控制器 22 串行地送到串联的各个存储装置,除了 CE# 和 RST#;CE# 和 RST#

是并行提供给所有存储装置的。如此, 附图 2B 的串行接口闪速存储装置接收具有其自己格式或协议的存储器控制信号, 用来执行其中的存储器操作。

[0059] 在共同拥有的 2008年2月15日申请的名称为"Clock Mode Determination in a Memory System"的美国专利公开第 20090039927 号中公开了附图 2 的串联连接存储系统的 更多细节,该美国专利公开文本介绍了包括各个存储装置接收并行时钟信号的串行存储器系统,和包括各个存储装置接收源同步时钟信号的串行存储器系统。

[0060] 同时拥有附图 1B 的异步闪速存储装置和附图 2B 的串行接口闪速存储装置使得存储系统制造商能够提供这两种类型的存储系统。不过,这有可能会为存储系统制造商带来更高的成本,因为必须要寻求和购买两种不同类型的存储装置。本领域技术人员都知道,采购量越大,单件存储装置的价格就越低,因此大量采购可以使得存储系统的成本最低。因此,虽然制造商能够提供两种类型的存储系统,但是它担负着风险,即当有一种类型的存储装置的市场需求非常高时,另一种类型的存储装置的市场需求会降低甚至退出市场。这可能会给他们留下无法使用的已经购买了的备用存储装置。

[0061] 如附图 1B 和附图 2B 所示,异步和串行接口闪速存储装置的功能端口分配或定义是彼此很不相同的,所以彼此是不兼容的。用于控制分立存储装置的信号集合所具有的功能端口定义和顺序或时序称为协议或格式。因此,异步和串联闪速存储装置响应于不同的存储器控制信号格式而进行操作。这意味着,附图 2B 的串行接口闪速存储装置不能用在多支路存储系统中,并且由此,附图 1B 的异步闪速存储装置不能用在串联连接的环形拓扑结构存储系统中。

[0062] 虽然附图 2A 和附图 2B 中所示的串行接口闪速存储装置的性能优于附图 1A 和 1B 的异步闪速存储装置,但是存储系统制造商可能不希望丢掉它们的异步闪速存储装置存货。此外,由于异步闪速存储装置在工业中的普遍使用,相对于诸如附图 2A 的串行接口闪速存储装置之类的不太为大家熟悉的闪速存储装置,异步闪速存储装置的价格比较便宜。目前,存储系统制造商并不掌握用最小的成本开销利用串联互连装置的性能优势的解决之道。

[0063] 至少一些实例实施方式提供高性能复合存储装置,该高性能复合存储装置采用多芯片封装 (MCP) 或系统级封装 (SIP) 形式,并具有高速接口芯片或桥接装置与分立存储装置结合。桥接装置为它所集成于其中的系统提供 I/0 接口,并且接收采用全局格式的全局存储器控制信号,并且将这些命令转换为与分立存储装置兼容的采用本机或本地格式的本地存储器控制信号。在提供由桥接装置的 I/0 接口给予的性能优势的同时,桥接装置可以实现分立存储装置比如 NAND 闪速装置的再利用。桥接装置可以被具体实现为在封装中与分立存储装置管芯集成在一起的分立逻辑管芯。

[0064] 在当前的例子中,全局格式是与附图 2A 和 2B 的串联闪速存储装置兼容的串行数据格式,并且本地格式是与附图 1A 和 1B 的异步闪速存储装置兼容的并行数据格式。不过,本发明的实施方式并不局限于上述示例格式,而是取决于复合存储装置中使用的分立存储装置的类型和复合存储装置所在的存储系统的类型,可以使用任何一对存储器控制信号格式。例如,存储系统的全局格式可以遵循开放式 NAND 闪速接口 (ONFi) 标准,并且本地格式可以遵循异步闪速存储装置存储器控制信号格式。例如,一个具体的 ONFi 标准是 ONFi 2.0规范。按照另外一种可选方案,全局格式可以遵循异步闪速存储装置存储器控制信号格式,

并且本地格式可以遵循 ONFi 2.0 规范格式。一般来说, ONFi 规范是多支路同步协议, 其中数据和命令与时钟同步地经由兼容存储装置的数据输入与输出端口提供给兼容存储装置。换句话说, ONFi 兼容存储装置可以与具有并行双向输入/输出端口的异步 NAND 闪速存储装置有一些相似性, 不过也有一个重要区别, 就是 ONFi 兼容装置接收时钟信号。

[0065] 附图 3A 是按照本实施方式的复合存储装置的框图。如附图 3A 所示,复合存储装置 100 包括桥接装置 102,该桥接装置 102 与四个分立存储装置 104 相连接。各个分立存储装置 104 可以是例如存储容量为 8Gb 的异步闪速存储装置,但是可以使用任何容量的分立闪速存储装置代替 8Gb 的装置。此外,复合存储装置 100 并不局限于具有四个分立存储装置。当桥接装置 102 被设计成支持复合存储装置 100 中最大数量的分立存储装置的时候,可以包括任何适当数量的分立存储装置。

[0066] 复合存储装置 100 具有用于接收全局命令的输入端口 GLBCMD\_IN,和用于传递所接收的全局命令和读出数据的输出端口 GLBCMD\_OUT。附图 3B 是图解说明按照本实施方式的全局命令的层次结构的示意图。全局命令 110 包括具有特殊格式的全局存储器控制信号 (GMCS) 112 和地址报头 (AH) 114。这些全局存储器控制信号 112 提供存储器命令和命令信号,比如针对附图 2B 的串行接口闪速存储装置的存储器控制信号。地址报头 114 包括系统层面和复合存储装置层面上使用的地址信息。这个附加地址信息包括用于选择执行存储器命令中的 op 码的复合存储装置的全局装置地址 (GDA) 116,和用于在所选择的复合存储装置中选择执行 op 码的特定分立装置的本地装置地址 (IDA) 118。总的来说,全局命令包括与一个格式对应的所有存储器控制信号,并且此外还包括选择或控制复合存储装置或其中的分立存储装置可能需要的地址信息。

[0067] 要注意,桥接装置 102 并不执行 op 码或者按照行和地址信息访问任何存储器位置。桥接装置 102 使用全局装置地址 116 来确定是否它被选择来转换所接收的全局存储器控制信号 112。如果选择了,则桥接装置 102 使用本地装置地址 118 来确定要把转换后的全局存储器控制信号 112 发送给哪一个分立存储装置。为了与全部四个分立存储装置 104 进行通信,桥接装置 102 包括四组本地 I/0 端口(未示出),各个端口与相应的分立存储装置连接,这将稍后讨论。各组本地 I/0 端口包括分立存储装置正确操作所需的所有信号,并且从而起到了本地装置接口的作用。

[0068] 读出数据由复合存储装置 100 中的或者前文给出的复合存储装置中的任何一个闪速存储装置 104 提供。具体地说,桥接装置 102 可以与存储系统的存储器控制器连接,或者与串联互连装置的系统中的另一个复合存储装置的另一个桥接装置连接。输入端口 GLBCMD\_IN 和输出端口 GLBCMD\_OUT 可以是封装引脚、其它物理导体或者用于向和从复合存储装置 100,具体来说向和从桥接装置 102,发送/接收全局命令信号和读数据的任何其它电路。桥接装置 102 因此具有与输入端口 GLBCMD\_IN 和输出端口 GLBCMD\_OUT 的相应连接,以实现与外部控制器的通信,比如附图 2A 的存储器控制器 22,或者实现与系统中另一个复合存储装置的桥接装置的通信。将会在附图 7 的实例实施方式中示出,很多复合存储装置可以彼此串联连接。

[0069] 附图 4 是按照一种实施方式的桥接装置 200 的框图,该桥接装置与附图 3A 中所示的桥接装置 102 相对应。桥接装置 200 具有桥接装置输入/输出接口 202、存储装置接口 204 和格式转换器 206。格式转换器 206 包括用于将包括全局命令和全局命令信号的具有

第一格式的全局存储器控制信号转换为第二格式的命令格式转换器 208,和用于将数据在第一格式和第二格式之间转换数据的数据格式转换器 210。命令格式转换器 208 此外还包括状态机(未示出),该状态机响应于第一格式的全局存储器控制信号,并按照第二格式控制分立存储装置,比如附图 3A 的分立存储装置 104。

[0070] 桥接装置输入/输出接口202与外部设备进行通信,比如,与另一个复合存储装置的存储器控制器进行通信。桥接装置输入/输出接口202从存储器控制器或另一个复合存储装置接收全局格式(比如串行命令格式)的全局命令。此外再参照附图3B,输入/输出接口202中的逻辑对全局命令110的全局装置地址116进行处理来确定全局命令110是否寻址到相应的复合存储装置,并且对全局命令110中的本地装置地址118进行处理以确定相应复合存储装置中的哪一个分立存储装置接收经过转换的命令;经过转换的命令包括0p码,还包括可选的行和列地址以及写数据。如果全局命令被寻址到与桥接装置200连接的分立存储装置,那么格式转换器206中的命令格式转换器208将提供0p码和命令信号以及任意行和地址信息的全局存储器控制信号112从全局格式转换为本地格式,并且将其发送到存储装置接口204。这一转换后的本地命令具有在功能上与全局格式的全局信号相应的本地信号。在某些情况下,响应于单个全局命令,可以发出多个本地命令,因为完成全局命令的操作可能需要多个本地命令。如果写数据是以例如串行数据格式提供给桥接装置输入/输出接口202包括串行到并行转换电路,用于提供并行格式的数据位。对于读出操作,桥接装置输入/输出接口202包括并行到串行转换电路,用于提供并行格式的数据位。对于读出操作,桥接装置输入/输出接口202包括并行到串行转换电路,用于提供串行格式的数据位。对于读出操作,桥接装置输入/输出接口202包括并行到串行转换电路,用于提供串行格式的数据位,以便从GLBCMD OUT 输出端口输出。

[0071] 假设全局格式和本地格式是已知的,因此命令格式转换器 208 中的逻辑被具体用来执行信号的逻辑转换,以便与分立存储装置 104 兼容。要注意,命令格式转换器 208 可以包括至少基本上与存储系统的存储器控制器的控制逻辑类似的控制逻辑,用于按照具有本机格式的存储器控制信号控制分立存储装置。例如,如果分立存储装置是异步存储装置,比如存储装置 16-1 到 16-4,则命令格式转换器 208 可以事实上包括与附图 1A 的存储器控制器 14 相同的控制逻辑。这意味着,命令格式转换器 208 中的控制逻辑向分立存储装置提供本地格式的存储器控制信号的时序和顺序。

[0072] 如果全局命令对应于数据写入操作,则格式转换器 206 中的数据格式变换器 210 将会把数据从全局格式转换为本地格式,并且将其发送到存储装置接口 204。读出或写入数据的比特位并不需要逻辑转换,因此数据格式变换器 210 保证了数据的比特位位置在第一数据格式和第二数据格式之间的正确映射。格式转换器 206 起到了用于存储来自分立存储装置的读出数据或来自桥接装置输入/输出接口 202 的写入数据的数据缓冲器的作用。因此,可以解决全局格式和本地格式之间数据宽度的失配问题。此外,由于数据格式变换器 210 的缓冲功能,可以解决分立存储装置和桥接装置 200 以及桥接装置 200 和其它复合存储装置之间数据传输率不同的问题。

[0073] 存储装置接口 204 然后将转换为本地命令格式的命令转送或发送到通过附图 3B 的全局命令110 中的本地装置地址 118 选定的分立存储装置。在本实施方式中,经过转换的命令是经由命令路径 212 提供的。在一种实施方式中,命令路径 212 包括连接在复合存储装置中的各个分立存储装置与存储装置接口 204 之间的 i 组专用的本地 I/0 端口 LCCMD-i 或者通道。变量 i 是与复合存储装置中分立存储装置的数量相对应的整数。例如,各个

LCCMD-i 通道包括附图 1B 和表 1 中所示的所有端口。在可供选用的另一种实施方式中,例如,LCCMD-i 通道包括 0NFi 兼容装置的所有端口,包括可以在命令格式转换器 208 的时钟电路中生成的时钟信号。时钟发生电路和技术在本领域中是公知的,并且在本实施方式中,可以包括时钟分频器或者倍频器,用来从单独一个"主"时钟信号生成具有期望频率的时钟信号。

[0074] 下面是在进一步参照附图 3A 的复合存储装置 100 的情形下,桥接装置 200 的实例操作的介绍。对于读出操作,全局命令,比如全局读出命令,是通过输入端口 GLBCMD\_IN 到达桥接装置输入/输出接口 202 的。这个全局读出命令包括针对要从与桥接装置 200 相连的分立存储装置 104 中读出的数据的全局存储器控制信号,这些全局存储器控制信号提供全局格式的 op 码和行与列信息。一旦桥接装置输入/输出接口 202 确定,它已经通过将全局装置地址 116 与复合存储装置 100 的预定地址相比较,为全局读出命令做出了选择,则命令格式转换器 208 就会把全局读出命令转换为与要在其上执行读出数据命令的分立存储装置 104 兼容的本地格式。后面将会介绍,复合存储装置可以具有一分配的地址。全局读出命令的本地装置地址 118 被转送到存储装置接口 204,并且经过转换的读出数据命令被经由相应的一组命令路径 212 的本地 I/0端口提供给由本地装置地址寻址到的分立存储装置。

[0075] 称为读出数据的数据被从选定的分立存储装置 104 中读出并且被以本地格式经由存储装置接口 204 的同一本地 I/0 端口提供给数据格式变换器 210。数据格式变换器 210 然后将读出数据从本地格式转换为全局格式并且通过桥接装置接口 202 的输出端口 GLBCMD\_OUT 将来自于选定分立存储装置 104 的读出数据提供给存储器控制器。桥接装置接口 202 包括内部切换电路,用于将来自于数据格式变换器 210 的读出数据或者输入端口 GLBCMD IN 接到输出端口 GLBCMD OUT 上。

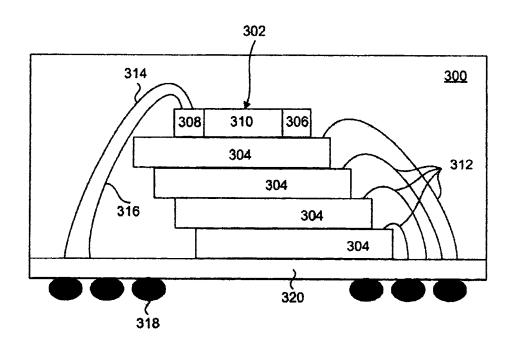

[0076] 前面介绍的附图 3A 是按照一种实施方式的复合存储装置的功能表达。附图 5表示按照本发明的另一种实施方式的制作为系统级封装(SIP)的复合存储装置,它相当于附图 3A 所示的复合存储装置。附图 5表示堆叠在封装中的复合存储装置的横截面。封装 300包括与附图 3A 的桥接装置 102 相对应的桥接装置 302 和分别与同样来自附图 3A 的分立存储装置 104 相对应的四个分立存储装置 304。在本实施方式中,这些装置是制成品半导体芯片或管芯。桥接装置 302 经由存储装置接口 306 以例如并行异步 NAND 格式这样的本地格式与存储装置 304 进行通信。桥接装置 302 以例如前面介绍的串行数据格式这样的全局格式经由桥接装置输入/输出接口 308 与存储器控制器(未示出)或与另一个复合存储装置的桥接装置进行通信。格式转换器 310包括前面提到的附图 3A 的命令格式转换器 208 和数据格式变换器 210,用于提供它自身与分立存储装置 304 之间的单向命令格式转换和双向数据格式转换。

[0077] 在当前示出的例子中,复合存储装置封装300称为SIP系统或多芯片封装(MCP)系统。该封装包封了桥接装置302和所有四个分立存储装置304。由线312代表的本地通信端子将各个分立存储装置304的I/0端口连接到桥接装置302的存储装置接口306。各条线312代表传送与本地格式相对应的所有信号的一条通道LCCMD-i。一个示例本地格式是包括表1中所示的信号的异步闪存存储器格式。由线314和316代表的全局通信端子将输入端口GLBCMD IN和输出端口GLBCMD OUT经由可选的封装基板320分别连接到封装引

线 318。桥接装置 302 和分立存储装置 304 彼此之间的相对物理排布取决于分立存储装置 304 焊盘的位置和桥接装置 302 焊盘的位置。

[0078] 在附图 5A 的实施方式中,各个分立存储装置 304 将其数据焊盘与桥接装置 302 的焊盘直接连接。各个分立存储装置 304 的数据焊盘形成一个通道,该通道可以与桥接装置 302 的专用对应数据焊盘连接。在附图 5B 所示的可供选用的另一种实施方式中,各个分立存储装置 304 通过封装基板 320 中形成的导电轨迹与桥接装置 302 连接。更加具体地讲,焊接线 312 通过这些形成在基板 320 内的导电轨迹与焊接线 314 电连接。在一种实施方式中,各个分立存储装置 304 经由诸如附图 5A 的实施方式中那样的各通道与桥接装置 302 的相应数据焊盘电连接。按照另外一种可选方案,桥接装置 302 仅包括一组与各个分立存储装置 304 的数据焊盘并联连接的数据焊盘。因此,在所有的分立存储装置 304 之间共享一个通道。在这种可供选用的实施方式中,基板 320 中形成的导电轨迹可以与桥接装置 302 和分立存储装置 304 并行相接,这称为多分支结构。

[0079] 在附图 5A 中目前所示的例子中,分立存储装置 304 是以它们的焊盘面朝上的方式放置的,并且以错开的阶梯样式彼此堆叠在一起以露出焊盘,从而不遮挡这些装置位于接近芯片边缘的位置上的焊盘。桥接装置 302 是以它的焊盘朝上的方式放置的,并且堆叠在叠层最上面的分立存储装置 304 之上。其它的构造也是可以的,取决于分立存储装置焊盘的放置方式,并且可以使用不同的通信端子来代替焊接线。例如,可以使用借助电感耦合技术的无线通信,或者可以使用硅穿孔 (TSV) 互连来代替焊接线。共同拥有的名称为"Method for Stacking Serially-Connected Integrated Circuits and Multi-Chip Device Made from Same"的美国专利公开第 20090020855 号展示了将芯片堆叠在一起的技术。而且,桥接装置 302 并不会对封装 300 中叠层的尺寸造成明显影响。由此,本领域技术人员应当清楚,复合存储装置 300 在较大的系统中仅占很小的面积,却能提供很高的存储量。

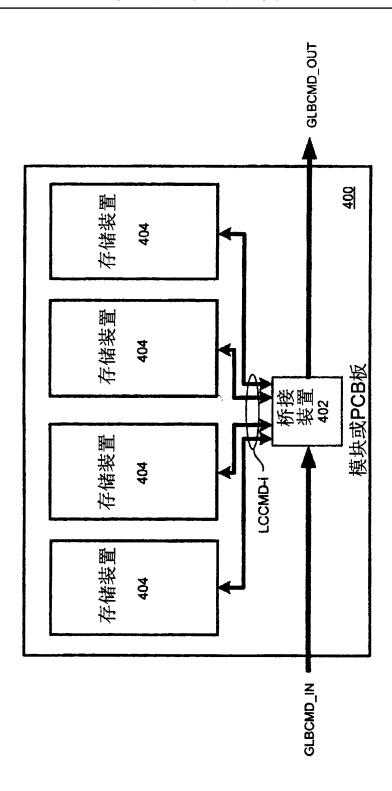

[0080] 附图 6 表示附图 3A 的复合存储装置的另一种实施方式,它被形成为一个模块或者形成在印刷电路板 (PCB) 上。如附图 6 中所示,复合存储装置 400 包括桥接装置 402 和四个分立存储装置 404。桥接装置 402 和分立存储装置 404 是封装的装置,意思是说它们各自包封了半导体管芯并且具有与 PCB 中预先制作好的导电轨迹焊接在一起的封装引线。桥接装置 402 经由为各个存储装置 404 组织为专用的本地 I/0 端口或通道 LCCMD-i 的导电轨迹与各个分立存储装置 404 连接。包括桥接装置的模块或 PCB 包括用于接收全局命令的输入端口 GLBCMD\_IN 和用于提供在输入端口处接收到的读出数据和全局命令的输出端口 GLBCMD\_OUT。这些输入和输出端口可以与控制器(未示出)或与另一个复合存储装置连接。如针对附图 5A 和 5B 的实施方式所介绍的那样,各个分立存储装置 404 可以各自与桥接装置 402 直接连接,或者按照另外一种可选方案,各个存储装置 404 可以与多支路结构中的桥接装置 402 并联连接。

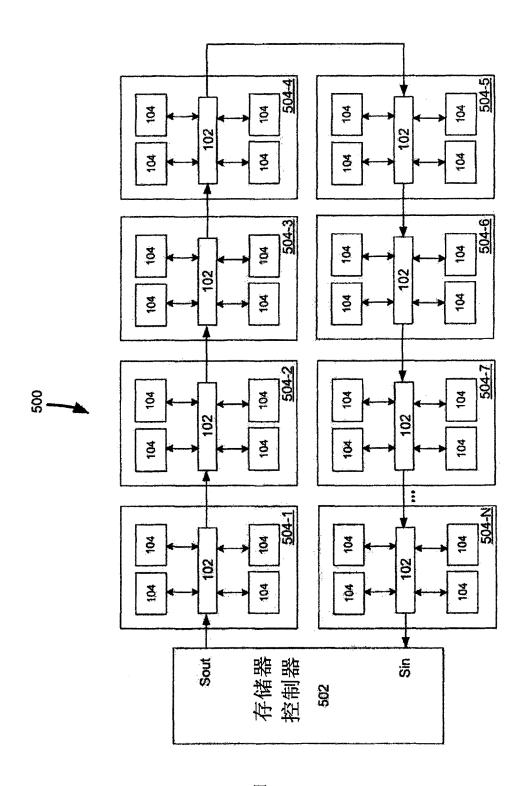

[0081] 附图 5A、5B 和附图 6 的复合存储装置实施方式可以用在另一种实施方式的存储系统中,比如附图 2A 的串行存储器系统中。因此,附图 7 的存储系统 500 与附图 2A 的串行存储器系统 20 相类似。存储系统 500 包括存储器控制器 502 和复合存储装置 504-1 到 504-j,其中 j 是整数。各个复合存储装置 504-1-504-j 与存储器控制器 502 串联连接。类似于附图 2A 的系统 20,复合存储装置 504-1 是存储系统 500 的第一个复合存储装置,因为它与存储器控制器 410 的输出端口 Sout 连接,并且存储装置 504-n 是最后一个装置,因为它与存储器控制器 410 的输出端口 Sout 连接,并且存储装置 504-n 是最后一个装置,因为它与存

储器控制器 410 的输入端口 Sin 相连接。复合存储装置 504-2 到 504-7 于是就是连接在第一个和最后一个复合存储装置之间的介于中间的串联连接的存储装置。Sout 端口提供全局格式的全局命令。Sin 端口接收全局格式的读出数据和全局命令,因为它通过所有的复合存储装置传播。

[0082] 附图 7 中所示的各个复合存储装置类似于附图 3A 中所示的复合存储装置 100。各个复合存储装置具有桥接装置 102 和四个分立存储装置 104。如前面所介绍的那样,各个复合存储装置中的各个桥接装置 102 与各分立存储装置 104 相连接,并且与存储器控制器 502 和/或串联环形拓扑结构或者串联互连构造中前一个或后一个复合存储装置连接。各个复合存储装置 504-1 到 504-j 的功能与之前针对附图 3A 和附图 4 的实施方式介绍的一样。

[0083] 在存储系统 500 中,各个复合存储装置被分配一个唯一的全局装置地址。可以将该唯一的全局装置地址存储在桥接装置 102 的装置地址寄存器中,并且更加具体地,可以存储在附图 4 中所示的桥接装置框图的输入/输出接口 202 的寄存器中。这个地址可以是使用装置地址分配方案在存储系统 500 加电阶段期间自动分配的,如名称为"Apparatus and Method for Producing Identifiers Regardless of Mixed Device Type in a Serial Interconnection"的共同拥有的美国专利公开第 20080192649 号中介绍的那样。此外,各个复合存储装置 504 可以包括用于存储与各个复合存储装置 504 中的分立存储装置的数量有关的信息的分立装置寄存器。如此,在操作的同一个加电阶段期间,存储器控制器能够查询各个分立装置寄存器并且记录各个复合存储装置内的分立存储装置的数量。由此,存储器控制器可以有选择地寻址存储系统 500 的各个复合存储装置 504 中的各个分立存储装置 104。

[0084] 下面使用选择复合存储装置 504-3 来执行存储器操作的例子来介绍存储系统 500 的操作。在本例中,存储系统 500 是类似于附图 2 中所示的系统的串联连接存储系统,并且各个分立存储装置 104 假设为异步 NAND 闪速存储装置。因此,各个复合存储装置 504-1 到504-j 中的桥接装置 102 被设计成用来接收由存储器控制器 502 发出的全局格式的全局命令和将它们转换为与 NAND 闪速存储装置兼容的本地格式。进一步假设已经加电并且已经为各个复合存储装置分配了地址。

[0085] 存储器控制器 502 从其 Sout 端口发出全局命令,它包括与复合存储装置 504-3 相对应的全局装置地址 116。第一复合存储装置 504-1 接收该全局命令,并且它的桥接装置 102 将它所分配的全局装置地址与该全局命令种的全局装置地址进行比较。因为全局装置地址不匹配,所以用于复合存储装置的桥接装置 102 忽略该全局命令并且将该全局命令传递到复合存储装置 504-2 的输入端口。由于复合存储装置 504-2 的所分配的全局装置地址与全局命令中的全局装置地址不匹配,因此在复合存储装置 504-2 中出现同样的动作。由此,该全局命令被传递到复合存储装置 504-3。

[0086] 复合存储装置 504-3 的桥接装置 102 确定它所分配的全局装置地址与全局命令中的全局装置地址之间的匹配。因此,复合存储装置 504-3 的桥接装置 102 开始着手将全局存储器控制信号转换为与 NAND 闪速存储装置兼容的本地格式。桥接装置然后将经过转换的命令发送给按照全局命令中包含的本地装置地址 118 选择的 NAND 闪速存储装置。所选择的 NAND 闪存装置然后执行与其接收到的本地存储器控制信号相应的操作。

[0087] 当复合存储装置 504-3 的桥接装置 102 在转换全局命令的时候,它将全局命令传递给下一个复合存储装置。剩余的复合存储装置忽视在存储器控制器 502 的 Sin 端口处最终接收到的全局命令 Sin。如果全局命令对应于读出操作,则所选择的复合存储装置 504-3 的 NAND 闪速存储装置以本地格式向其对应的桥接装置 102 提供读出数据。桥接装置 102 然后将读出数据转换为全局格式,并且通过输出端口将其传递到下一个复合存储装置。所有剩余复合存储装置的桥接装置 102 将读出数据送到存储器控制器 502 的 Sin 端口。本领域技术人员应当理解,可以发出其它的全局命令来执行读出操作,所有这些全局命令都要由所选择的复合存储装置 102 的桥接装置 102 加以转换。

[0088] 在本实施方式中,全局命令被传送到存储系统 500 中的所有复合存储装置。按照另一种可供选用的实施方式,桥接装置 102 包括额外的逻辑,用于阻止将全局命令传送到存储系统 500 中的更多复合存储装置。更加具体地讲,一旦所选择的复合存储装置确定全局装置指向的是它,则相应的桥接装置 102 驱动它的输出端口到一个空值,比如例如 VSS或 VDD 的固定电压电平。因此,剩余的未被选择的复合存储装置就节省了切换电力,因为它们将不执行全局命令。在名称为"Apparatus and Method for Producing Identifiers Regardless of Mixed Device Type in a Serial Interconnection"的共同拥有的美国专利公开第 20080201588 号中介绍了这种用于串联连接存储系统的节电方案的细节,该美国公开文本的全部内容以引用的方式整体并入本文。

[0089] 前面介绍的附图 7 的实施方式图解说明的是各个复合存储装置 504-1 到 504-n 中都有相同类型的分立存储装置的存储系统,比如都有例如异步 NAND 闪速存储装置这称为同质存储系统,因为所有的复合存储装置都是相同的。在另一种可供选择的实施方式中,可以是异质存储系统,就是其中不同的复合存储装置具有不同类型的分立存储装置。例如,一些复合存储装置包括异步 NAND 闪速存储装置,而其它一些可以包括 NOR 闪速存储装置。在这一另一种可供选用的实施方式中,所有的复合存储装置都采用相同的全局格式,但是在内部,各个复合存储装置具有其桥接装置 200,桥接装置 200 的作用是将全局格式的存储器控制信号转换为与 NOR 闪速存储装置或 NAND 闪速存储装置相对应的本地格式的存储器控制信号。

[0090] 在再另一种实施方式中,单独一个复合存储装置可以具有不同类型的分立存储装置。例如,单独一个复合存储装置可以包括两个异步 NAND 闪速存储装置和两个 NOR 闪速存储装置。这种"混合"或"异质"复合存储装置可以采用前面介绍的相同的全局各式,但是在内部,其桥接装置被设计成用来将全局格式的存储器控制信号转换为与 NOR 闪速存储装置和 NAND 闪速存储装置相对应的本地格式的存储器控制信号。

[0091] 这样的桥接装置可以包括用于 NAND 闪速存储装置和 NOR 闪速存储装置二者各自的专用格式转换器,专用格式转换器可以通过前面介绍的全局命令中提供的地址信息来选择。如参照附图 3B 介绍的那样,地址报头 114 包括系统层面和复合存储装置层面上使用的地址信息。这个附加地址信息包括用于选择执行存储器命令中的 op 码的复合存储装置的全局装置地址 (GDA) 116,和用于在所选择的复合存储装置中选择执行 op 码的特定分立装置的本地装置地址 (LDA) 118。桥接装置可以具有使用 LDA118 来确定应当将全局命令送到两个格式转换器中的哪个格式转换器的选择器。

[0092] 在存储系统 500 的另一种可供选用的实施方式中,复合存储装置可被用在多支路

配置的存储系统中,比如附图 1A 所示的多支路存储系统。在这一实施方式中,各个复合存储装置彼此之间和与存储器控制器之间经由单独一个通道并联连接,比如附图 1A 的通道 18。由此,各个复合存储装置的桥接装置被构成为用来通过数据输入与输出端口(比如附图 1B 的数据输入/输出端口 I/O[n])接收命令和数据,同时通过同一数据输入/输出端口提供读出数据。在一个例子中,各个复合存储装置的桥接装置被构成为用来接收异步控制信号或同步控制信号。对于同步控制信号,存储器控制器提供由各个复合存储装置的桥接装置接收到的源同步时钟信号。在本实施方式的例子中,桥接装置被构成为用来接收 ONFi 标准命令,ONFi 标准命令可以由桥接装置转换为与分立存储装置兼容的格式。

[0093] 为了改善复合存储装置相对于分立存储装置的总体读和写性能,桥接装置被构成为用来以大于分立存储装置的最大额定频率的频率接收写入数据和提供读出数据。不过,取决于复合存储装置内选用的分立存储装置,它们可能不能足够快地将其读出数据实时提供给桥接装置,从而桥接装置不能以其较高的速度输出读出数据。类似地,虽然可以以高速向桥接装置提供写入数据,但是分立存储装置可能具有过低的写入速度。因此,为了补偿速度上的这一不匹配,桥接装置包括虚拟页缓冲器,用来临时存储从分立存储装置的页缓冲区中读出或者要写入到分立存储装置的页缓冲区中去的数据页的至少一部分。按照本实施方式,这些虚拟页缓冲器包括用于存储来自分立存储装置的读出数据或者要写入到分立存储装置中的写入数据的存储器。在例如附图 4 的实施方式中,数据格式转换器 210 包括这一存储器,它可以是公知的存储器,比如例如 SRAM或 DRAM。虚拟页缓冲器的更多细节将参照附图 8 中所示的实施方式加以介绍。

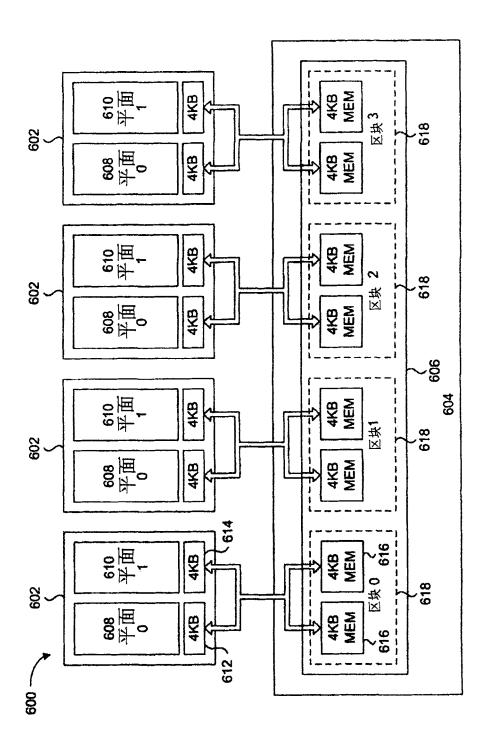

[0094] 附图 8 是复合存储装置 600 的框图,图解说明了四个 NAND 闪速存储装置的页缓冲区与桥接装置的存储器之间的关系。复合存储装置 600 类似于附图 3A 中所示的复合存储装置 100,并且在附图 8 的实例实施方式中包括四个 NAND 闪速存储装置 602 和桥接装置 604。桥接装置 604 被表示为附图 4 的桥接装置 400 的简化形式,其中仅示出了存储器 606。附图 8 中省略了桥接装置 400 的其它部件,但是应当理解为这些部件是存在的,这样才能确保桥接装置 600 的正确操作。后面将会讨论到,存储器 606 在逻辑上被分成了与四个 NAND 闪速存储装置 602 中每一个的页缓冲区相对应的组。

[0095] 各个 NAND 闪速存储装置 602 具有被组织为两个平面 (plane) 608 和 610 的存储器阵列,分别标为"平面 0"和"平面 1"。虽然没有示出,但是穿过各个平面 608 和 610 水平延伸的行电路驱动字线,和可以包括列访问和读出电路的页缓冲区 612 和 614,与穿过各个平面 608 和 610 垂直延伸的位线连接。这些电路的用途和功能是本领域技术人员所熟知的。对于任何读出或写入操作,跨越两个平面 608 和 610 驱动一个逻辑字线,意思是说,一个行地址驱动两个平面 608 和 610 中的同一个物理字线。在读出操作中,存储在与所选择的逻辑字线相连的存储器基元中的数据被读出并存储在页缓冲区 612 和 614 中。类似地,写入数据被存储在页缓冲区 612 和 614 中,用来编写到与所选择的逻辑字线相连的存储器基元中。

[0096] 桥接装置 604 的存储器 606 被分成为逻辑或物理子存储器 616,这些子存储器 616 各自具有与页缓冲区 612 或 614 至少相同的存储空间。逻辑子存储器可以是存储器的物理块中指定的在地址空间,而物理子存储器是具有固定地址空间的明确形成的存储器。子存储器 616 划分成存储器区块 618,标为 Bank0 到 Bank3,其中存储器区块 618 的子存储器 616

仅与一个 NAND 闪速存储装置 602 的页缓冲区相关联。换句话说,存储器区块 618 的子存储器 616 专用于 NAND 闪速存储装置 602 的各页缓冲区 612 和 614。在读出操作期间,页缓冲区 612 和 614 中的读出数据被传送到相应存储器区块 618 的子存储器 616 中。在编程操作期间,存储在存储器区块 618 的子存储器 616 中的写入数据被传送到相应 NAND 闪速存储装置 602 的页缓冲区 612 和 614 中。要注意的是,NAND 闪速存储装置 602 可以具有单独一个平面或者不止两个各个具有相应页缓冲区的平面。因此,存储器 606 应该被相应地组织为具有专用于各个页缓冲区的子存储器。

[0097] 当前附图 8 的例子具有总共有 8KB 页缓冲区空间的 NAND 闪存装置 602,这 8KB 页缓冲区空间被组织为两个分立的 4KB 页缓冲区。各个分立的 4KB 页缓冲区与各平面(比如例如平面 608 或平面 610)的位线相接。本领域技术人员都知道,页缓冲区的大小随着 NAND 闪速存储装置的总容量的增加而逐渐增加,这样未来的 NAND 闪存装置可能会具有更大的页缓冲区。更大的页缓冲区能够实现更快的总体读出和程控操作,因为 NAND 闪速存储装置的内核读出和程控时间基本上时恒定不变的,并且与页缓冲区大小无关,这是本领域技术人员公知的。与一半大小的页缓冲区比较,更大的页缓冲区能够允许在需要另一个内核读取操作以访问存储器阵列不同行中的另一个数据页之前以相对稳定的两倍的数据读取进行突发读取。类似地,在需要将另一页写入数据加载到页缓冲区之前,同时可以以两倍的写入数据将写入数据编程到存储器阵列。因此,较大页缓冲区适合于音乐或视频数据可能有数页大小的多媒体应用。

[0098] 在附图 8 的复合存储装置 600 中,总内核读出时间包括 NAND 闪速存储装置内核读出时间,之前称为 Tr,加上传送时间 Ttr。传送时间 Ttr是 NAND 闪速存储装置输出或读出页缓冲区 612 和 614 的内容,从而它们可以被写入到一个存储器区块 618 的相应子存储器616 中所需的时间。总内核编程时间包括编程传送时间 Ttp 加上 NAND 闪速存储装置内核编程时间(之前称为 Tpgm)。编程传送时间 Ttp 是桥接装置 608 输出或读出一个存储器区块 618 的子存储器 616 的内容,从而它们可以在编程操作之前被加载到 NAND 闪速存储装置602 的相应的页缓冲区 612 和 614 中所需的时间。对于多媒体应用,可以跨越不同的 NAND 闪速存储装置存储数据并且可以在与另一个 NAND 闪速存储装置 602 相对应的数据正在由桥接装置 604 输出的时候同时操作数据来遮掩一个 NAND 闪速存储装置的内核操作。例如,在从一个存储器区块 618 中突发读取数据时,内核读出操作可以已经在进行中,用来自另一个 NAND 闪速存储装置 602 的数据加载另一个存储器区块 618 的子存储器 616。

[0099] 可能会有文件大小小于 NAND 闪速存储装置页缓冲区的整页大小的应用。这些文件包括文本文件和个人计算机桌面应用程序中通常使用的其它类似数据类型的文件。用户一般情况下会将这些文件复制到通常使用 NAND 闪存存储器的通用串行总线 (USB) 非易失性存储驱动器中。另一种出现的应用是固态驱动器 (SSD),固态驱动器 (SSD) 可以代替磁盘驱动器 (HDD),但是使用 NAND 闪存存储器或其它非易失性存储器来存储数据。复合存储装置读出和编程顺序与之前介绍的相同,同时有以下区别。这个例子假设期望的数据小于整页大小,并且与其它数据一起存储在页中。对于读出操作,在所有的页缓冲区数据已经从所选择的 NAND 闪速存储装置 602 的页缓冲区 612 和 614 传递到了相应的子存储器 616 之后,使用列地址来定义存储在存储器区块 618 的子存储器 616 内的期望数据的第一位和最后一位的位置。然后仅仅从桥接装置 604 的子存储器 616 中读出第一个、最后一个和介于中间

的数据位。

[0100] 在这种情形下传送时间 T 耐于某些应用可能是无法接受的,因为它明显增大了复合存储装置的总内核读出时间。这些应用包括读出操作应当被尽快执行的 SSD。虽然对于任何页缓冲区大小,NAND 闪速存储装置的内核读出时间 Tr 都是保持恒定的,但是将整个内容传送到子存储器 616 的传送时间 Ttr 直接取决于页缓冲区大小。

[0101] 按照本实施方式,复合存储装置的传送时间 Ttr 可以通过将存储器区块 618 的子存储器 616 配置为具有虚拟最大页面大小(称为虚拟页大小)而得以最小化,该虚拟最大页面大小小于复合存储装置内的 NAND 闪速存储装置的页缓冲区的最大物理大小。基于针对特定存储器区块 618 的虚拟页面大小配置,桥接装置 604 发出读出命令,此时仅有与页缓冲区中存储的虚拟页大小相对应的数据中的一段被传送到相应的子存储器 616。页缓冲区的这一段称为页段。

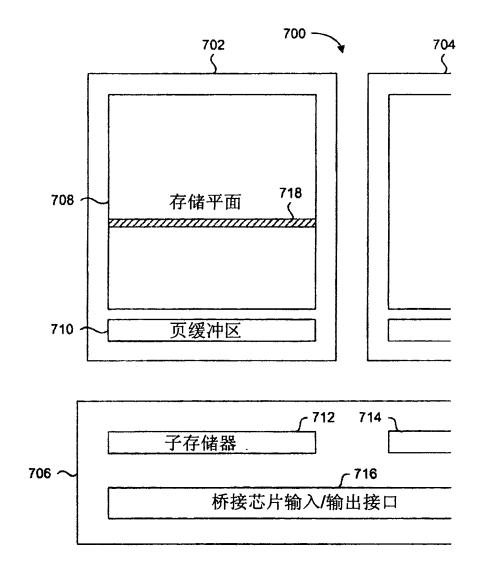

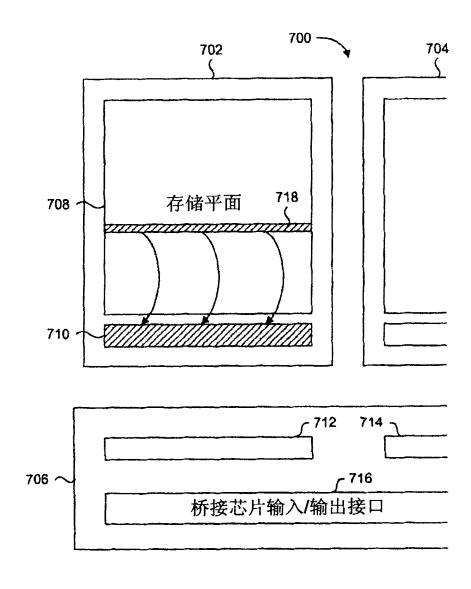

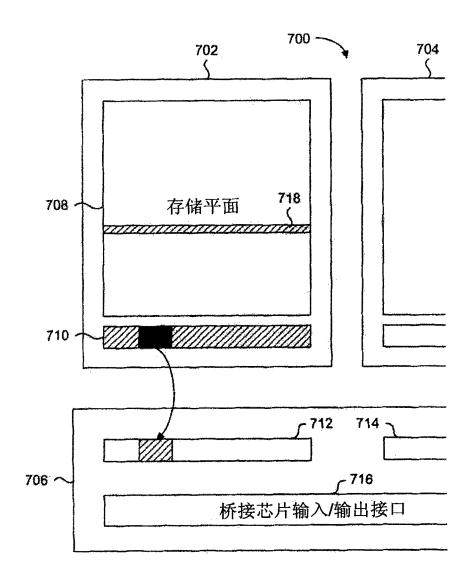

[0102] 附图 9A 到 9C 图解说明了如何按照本发明的实施方式从复合存储装置的诸如闪速存储装置之类的分立存储装置中读出与一组虚拟页大小相对应的数据。附图 9A 到 9C 表示具有一个完全示出的第一NAND 闪速存储装置 702、一部分第二 NAND 闪速存储装置 704 和一部分桥接装置 706 的复合存储装置 700。这个例子的 NAND 闪速存储装置具有单独一个平面 708,该平面 708 具有与单独一个页缓冲区 710 相连接的位线。示出的桥接装置 706 部分包括第一子存储器 712、第二子存储器 714 和桥接装置输入/输出接口 716。第一子存储器 712 对应于与第一 NAND 闪速存储装置 702 相关联的第一存储器区块,而第二子存储器 714 对应于与第二 NAND 闪速存储装置 704 相关联的第二存储器区块。为了解释本例中的读出操作,假设要访问来自于第一 NAND 闪速存储装置 702 的数据,并且第一存储器区块(第一子存储器 712)的虚拟页大小已经被配置为小于页缓冲区 710 的最大物理大小。

[0103] 从附图 9A 开始,假设桥接装置 706 已经接收了代表访问第一 NAND 闪速存储装置 702 中存储的数据的读出操作的全局存储器控制信号,并且已经对适当的本地存储器控制信号进行了编码并且将其提供给了第一 NAND 闪速存储装置 702。响应于与读出命令相对应的本地存储器控制信号,第一 NAND 闪速存储装置 702 启动按照本地存储器控制信号中的地址信息选择的行或字线 718。继续参考附图 9B,当字线 718 被启动或者被驱动到对访问与其连接的存储器基元的存储数据有效的电压电平上时,由页缓冲区 710 内的感测电路感测在与各个所访问的存储器基元相连的位线上生成电流或电压。这样,所访问的存储器基元的数据状态就被存储在页缓冲区 710 中。在附图 9C 中,NAND 闪速存储装置 702 将页缓冲区 710 的特定范围的位位置内存储的数据输出到桥接装置 706,并且具体输出到第一子存储器 712。这一数据输出处理是在达到 NAND 闪速存储装置 702 的最大额定速度或者数据速率的情形下执行的。

[0104] 在这一实例 NAND 闪速存储装置 702 中,一旦 NAND 闪速存储装置 702 报告或通知 桥接装置 706 来自所选择的行 718 的读出数据被保存到了页缓冲区 710,通常是借助就绪 / 忙信号来报告或通知的,就会由桥接装置 706 自动提供包括与这一特定范围的位位置相对应的列地址的突发读出命令。该列地址是根据为第一子存储器 712 配置的虚拟页大小来确定的。然后以较高的速度或数据速率经由桥接装置输入 / 输出接口 716,通过复合存储装置 700 的输出数据端口输出第一子存储器 712 中存储的数据。在本实施方式中,输出数据端口包括与之前表 2 中所示的 Q[n] 数据输出端口相对应的引脚或引线。

[0105] 因此可以看出,通过将第一子存储器 712 的虚拟页大小设置为小于页缓冲区 710 的最大物理大小,仅有相应大小的数据页段从页缓冲区 710 中输出到第一子存储器 712。这个页段包括特定范围的位位置,每个位位置都是可由列地址寻址的。稍后将会讨论,页段是可寻址的。由此,相对于将页缓冲区 710 的所有数据传送到第一子存储器 712 的情形,可以明显减小 NAND 闪速存储装置 702 输出来自于页缓冲区 710 的这一数据页段的传送时间 Ttr。

[0106] 前面提到的例子图解说明的是如何使传送时间 Ttr 最小。将虚拟页的大小设置为小于页缓冲区 710 的最大物理大小在写入操作期间也可以提供相同的性能优点。在写入操作中, 附图 9A 到 9C 所示的顺序实际上是反过来的。例如, 由桥接装置输入/输出接口 716 接收写入数据并且将写入数据写入到子存储器中, 比如写入到第一子存储器 712 中。这一写入数据具有与预定的虚拟页大小相匹配的大小, 然后将该写入数据传送到页缓冲区 710。将这一写入数据从桥接装置 706 传送到页缓冲区 710 所需的时间是传送时间 Ttr, 它取决于写入数据的大小和 NAND 闪存装置 702 的工作频率。写入数据被存储在页缓冲区 710 的称为页段的特定位位置内, 并且通过响应于页缓冲区 710 中存储的写入数据来激活选定行718 和向位线施加所需的编程电压, 启动 NAND 闪存装置 702 的内核编程操作。因此, 通过缩短写入操作期间的传送时间 Ttr, 存储系统的总写入时间得到了减小。

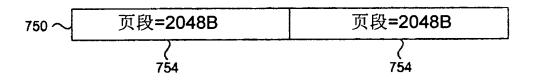

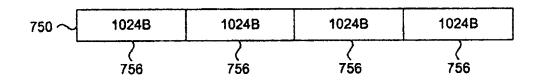

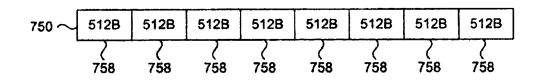

[0107] 按照本实施方式,通过可识别的命令,桥接装置706的第一子存储器712可被配置为具有任何一个预设的虚拟页大小的容量。一旦配置了第一子存储器712的虚拟页大小,相应NAND闪速存储装置的页缓冲区710就在逻辑上被分成多个大小相等的与所配置的虚拟页大小相对应的页段。附图10A到10D是基于所配置的虚拟页大小具有不同大小页段的NAND闪速存储装置页缓冲区750的示意图。要注意,页段代表页缓冲区750中的虚拟地址空间。在目前附图10A到10D的例子中,NAND闪速页缓冲区和桥接装置的子存储器都具有最大4K的物理大小。在附图10A中,虚拟页大小(VPS)被设置为最大或者全部4K,从而仅有一个页段752。在附图10B中,VPS被设置为2K,结果得到两个2K的页段754。在附图10C中,VPS被设置为1K,结果得到四个1K的页段756。在附图10D中,VPS被设置为612字节(B),结果得到大小为612B的八个页段758。本领域技术人员将会理解,即使更小大小的VPS和相应的页段也是可行的,并且页段的总数取决于NAND闪速存储装置页缓冲区750的最大大小。

[0108] 如前面针对本实施方式所讨论的,在NAND闪速存储装置的页缓冲区750之后已经加载了用于读出操作的数据,仅仅将页缓冲区750的页段输出到桥接装置。可以将期望的数据存储在页缓冲区750的一个特定页段中。因此可以由全局命令中提供的虚拟页地址为桥接装置对各个页段进行寻址。例如,使用两个地址位来选择附图10C中四个页段756之一。一旦选择了,期望的数据可能不会占据所选择的页缓冲区750页段中所有的位位置。如此,使用虚拟列地址在选定页段内选择第一位位置,要从这个第一位位置读出读出数据,一般情况下是在突发读出操作中读出的。下面表3根据附图10A到10D所示的实例页段概括了示例寻址方案。

[0109] 表 3

[0110]

| 虚拟页大小配置 | 页段的数量 | 对页段进行寻址<br>的位(VPA) | 对各个页段中的位位置进<br>行寻址的位(VCA) |

|---------|-------|--------------------|---------------------------|

| 4096B   | 1     | N/A                | 12                        |

| 2048B   | 2     | 1                  | 11                        |

| 1024B   | 4     | 2                  | 10                        |

| 612B    | 8     | 3                  | 9                         |

[0111] 表 3 中以举例的方式示出了示例寻址方案,但是本领域技术人员应当知道,取决于 NAND 闪速存储装置的页缓冲区的大小,可以使用不同的选址方案。如表 3 中所示,各个寻址方案包括用于对两个或更多个页段寻址的第一数量的位和用于对所选择的页段中的列寻址的第二数量的位。第一数量的位称为虚拟页地址(VPA),第二数量的位称为虚拟列地址(VCA)。虚拟页地址和虚拟列地址合在一起简称为虚拟地址。在本实施方式中,各个子存储器或子存储器区块的 VPS 配置对于存储器控制器或对于请求读出数据和向复合存储装置提供写入数据的另一主机系统是已知的。因此,按照相应的寻址方案,在全局命令中向复合存储装置提供用于从 NAND 闪速存储装置的页缓冲区中读出页段的虚拟地址,以便访问其中特定的 NAND 闪速存储装置。包括表 3 中所示的寻址方案在内的可行的寻址方案可以用于对页缓冲区的虚拟或逻辑地址空间进行寻址。虽然已经将这一逻辑地址空间描述为附图 10A 到 10D 的页缓冲区 750 中页段的位位置,但是实际的页缓冲区是用真实的物理地址寻址的。逻辑地址到物理地址的映射在本领域中是公知的。

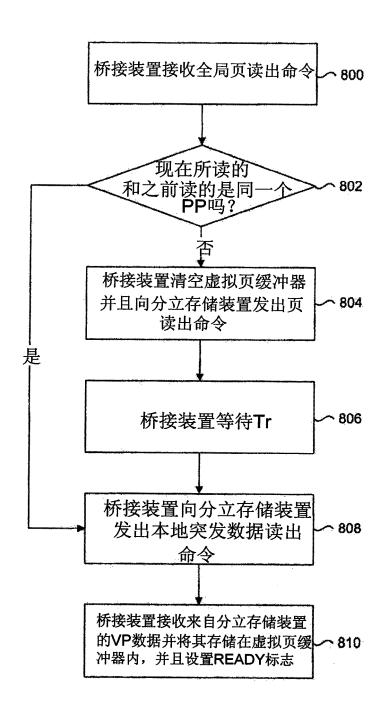

[0112] 下面讨论的是按照本发明的实施方式的从分立存储装置中读出数据和向分立存储装置写入数据的方法。附图 11 是描述按照本发明的实施方式的从复合存储装置中读出数据的方法的流程图, 附图 12 是描述向复合存储装置写入数据的方法的流程图。

[0113] 在目前介绍的附图 11 的方法中,假设选择了复合存储装置的一个特定分立存储装置来从中读出数据。此外还假设所选择的分立存储装置已经被配置为具有特定的虚拟页大小配置。该方法从步骤 800 开始,在步骤 800 中,桥接装置接收全局页读出命令,以从所选择的分立存储装置的物理页 (PP) 中的特定虚拟页 (VP) 中读出数据。在本例子中,PP = A 并且 VP = X,其中 A 代表存储器页的物理地址,X 代表构成物理页的所有虚拟页中的特定虚拟页。桥接装置将全局读出命令转换成本地读出命令,并且将其发送到所选择的分立存储装置。分立存储装置接收 PP = A 处的本地页读出命令,并且启动内核读出操作。在步骤802,如果当前读出操作针对的是新的 PP,那么该方法继续进行步骤804。在步骤804,桥接装置清空其虚拟页缓冲器,这可以包括将所有它们的状态设置为逻辑"1"或"0"电平。在步骤806,桥接装置于是等待为分立存储装置规定的内核读出时间Tr,以将数据在PP = A 处加载到其页缓冲区中。继续进行到步骤808,一旦内核读出时间Tr已过,桥接装置向分立存储装置发出本地突发数据读出命令。作为响应,分立存储装置在步骤808向桥接装置输出与VP = X 对应的列地址范围内存储的数据,桥接装置将这一数据存储到它的虚拟页缓冲器中。在步骤808中,桥接装置设置READY标志,以向主机系统或存储器控制器表明虚拟页缓冲器中存储的数据现在可以读出。

[0114] 回到步骤 802,如果当前读出操作针对的是前一个读出操作的同一个 PP,即 PP = A,则该方法跳到步骤 808,在步骤 808 桥接装置向分立存储装置发出突发数据读出命令。作为响应,分立存储装置输出 VP = Y。例如,如果这一随后的读出操作针对的是 PP = A 和 VP = Y,其中 Y 代表不同于 X 的特定虚拟页,那么就不需要分立存储装置内核读出操作,因为它的页缓冲区已经存储了 P = A 的整个数据内容,这包括与 VP = X 和 VP = Y 二者对应的数据。在这种情形下,分立存储装置仅仅需要输出与 VP = Y 相应的列地址范围内存储的数据,该数据在步骤 808 由桥接装置的虚拟页缓冲器接收和保存。响应于所设置的 READY 标志,存储器控制器可以发出输出虚拟页缓冲器中存储的数据的全局突发数据读出命令。

[0115] 在上述的读出方法实施方式中,从 PP = A 读出 VP = X 和 VP = Y 可以是相继发生的。具体地说,执行步骤 800 到 810 来从复合存储装置中读出 VP = X,随后的另一个读出操作仅仅涉及步骤 800、802、808 和 810,用来读出 VP = Y。按照附图 11 中所示的读出方法的另一种可供选用的实施方式,可以在第一突发数据读出命令之前发出针对 VP = Y 的第二页读出命令。这样,VP = Y 所对应的数据在分立存储装置和桥接芯片之间的传递可以在从桥接装置输出 VP = X 所对应的数据的同时发生。

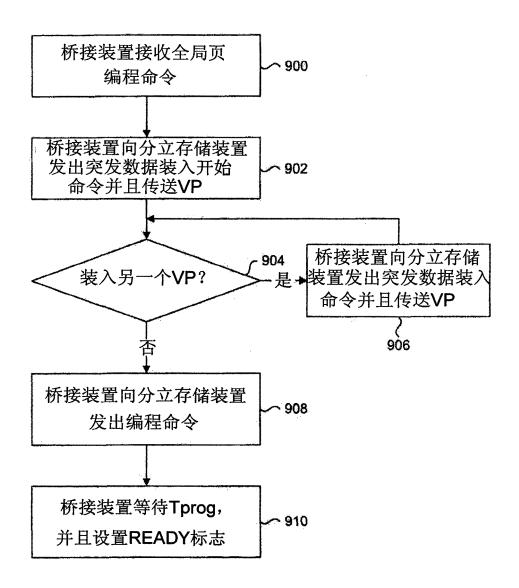

[0116] 现在介绍按照本实施方式的将数据写入到复合存储装置中的方法。在附图 12 的方法中,假设选择了复合存储装置的一个特定分立存储装置来将数据写入到其中。此外还假设分立存储装置已经被配置为具有特定的虚拟页大小配置。该编程方法起始于步骤 900,其中由桥接装置接收全局页编程命令。在这个例子中,数据被写入到 PP = A,并且该数据与 VP = X 相对应。步骤 900 一旦接收到页编程命令,则桥接装置的虚拟页缓冲器就会被加载要加以编程的数据 (VP = X)。在步骤 902,桥接装置发出向分立存储装置突发数据载入开始命令,然后将 VP = X 传送到分立存储装置。随后在步骤 904,如果要写入与 PP = A 的另一个虚拟页相应的数据,则该方法继续进行到步骤 906,在步骤 906,桥接装置向分立存储装置发出另一个突发数据载入命令。这个命令将与另一个虚拟页(比如 VP = Y)相对应的数据传递到分立存储装置。该方法从步骤 906 返回到到步骤 904。

[0117] 如果在 PP = A 中没有其它更多的虚拟页要加以编程,那么该方法继续进行到步骤908,在步骤908,桥接装置向分立存储装置发出编程命令。这会启动分立存储装置内的内核编程操作,以对分立存储装置的数据(比如 VP = X 和 / 或 VP = Y 到 PP = A)编程。随后在步骤910,桥接装置等待内核编程时间 Tprog 过去,并且然后设置 READY 标志,这向存储器控制器表明 VP = X 和 VP = Y 到 PP = A 的编程操作完成。

[0118] 前面介绍的复合存储装置的实施方式展示了如何使用具有第二和不同格式的全局存储器控制信号控制可以响应于一种格式的存储器控制信号的分立存储装置。另外一种可选的实施方式,桥接装置 200 可以被设计成用来接收具有一种格式的全局存储器控制信号,以便向分立存储装置提供具有相同格式的本地存储器控制信号。换句话说,这一复合存储装置被配置为用来接收用于控制分立存储装置的存储器控制信号。这样的配置使得多个分立存储装置可以各自起到独立于复合存储装置中的其它分立存储装置工作的存储器区块的作用。因此,各个分立存储装置可以从桥接装置 200 接收到它的命令,并且基本上彼此并行地继续进行操作。这也称作并行操作。桥接装置 200 的设计因此得到了简化,因为不再需要命令转换电路。

[0119] 前面介绍的实施方式图解说明了复合存储装置中的分立存储装置如何对不兼容

地命令格式做出响应。这是通过桥接装置将所接收到的全局命令转换为与分立存储装置兼容的本机命令格式来实现的。举例来说,可以将串行命令格式转换为异步 NAND 闪存格式。这些实施方式并不局限于这两个格式,因为任何一对命令格式都可以被从一种转换为另一种。

[0120] 在前面的介绍中,为了解释说明的目的,给出了许多的细节,以便实现对本发明实施方式的透彻理解。不过,对于本领域技术人员而言显而易见的是,并不需要这些具体细节来具体实现本发明。在其它一些情况下,以框图的形式示出公知的电子结构和电路,为的是避免本发明不清楚。

[0121] 应当理解,当本文中将一个单元称为与另一个单元连接或相接时,它可以是直接连接或接合到另一个单元上,也可以在它们之间还存其它单元。与此相反,当本文中将一个单元称为与另一个单元"直接连接"或"直接接合"时,就不存在介于二者之间的单元。用于描述单元之间关系的其它词句应当以类似的方式加以理解(即"之间"与"直接之间","相邻"与"直接相邻"等)。

[0122] 本申请中的附图并不是按比例画出的。例如,在附图 5 中,桥接装置 302 和分立存储装置 304 的相对大小并不成比例,并且成品桥接装置在面积上的量级要小于分立存储装置 304。

[0123] 可以对所介绍的实施方式进行某些改造和改变。因此,前面讨论的实施方式被认为是说明性的,而非限定性的。

图 1A

图 2B

图 3A

图 3B

图 4

图 5A

图 5B

图 6

图 7

图 8

图 9A

图 9B

图 9C

# 最大虚拟页缓冲区=NAND物理页缓冲区 750 ~ 页段=整页=4096B 752

图 10A

图 10B

图 10C

图 10D

图 11

图 12