## (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 103475314 B (45)授权公告日 2018.05.01

(21)申请号 201310419522.0

(22)申请日 2013.09.13

(65)同一申请的已公布的文献号 申请公布号 CN 103475314 A

(43)申请公布日 2013.12.25

(73)专利权人 上海集成电路研发中心有限公司 地址 201210 上海市浦东新区张江高斯路 497号

(72)发明人 李琛 蒋宇 吕本强

(74)专利代理机构 上海天辰知识产权代理事务 所(特殊普通合伙) 31275

代理人 吴世华 林彦之

(51) Int.CI.

*H03F* 1/26(2006.01)

#### (56)对比文件

CN 102594269 A, 2012.07.18,

CN 102684641 A,2012.09.19,

CN 102868377 A,2013.01.09,

审查员 周瑞瑞

权利要求书1页 说明书4页 附图3页

#### (54)发明名称

低噪声放大器

#### (57)摘要

本发明公开了一种低噪声放大器,其包括输入阻抗匹配电路、放大电路和输出阻抗匹配电路,其中所述输入阻抗匹配电路,其包含有源电感电路,用于匹配不同频率下的输入阻抗,其包括:第一NMOS管,其源极连接第三电流源,漏极接电压源;第二NMOS管,其漏极连接第二电流源及第一NMOS管的栅极;第三NMOS晶体管,其漏极与第二NMOS管的源极相连,栅极与第一NMOS管的栅极以及第四NMOS管,其漏极与第二NMOS管的栅极以及第四NMOS管,其漏极与第三NMOS管的栅极以及第一电流源相连,栅极与第三NMOS管源极相连,漏极接地;放大电路与有源电感电路及输出阻抗匹配电路相连。本发明的低噪声放大器可在不同频率下,实现信号放大。

CN 103475314 B

1.一种基于有源电感的低噪声放大器,其包括输入阻抗匹配电路、放大电路和输出阻抗匹配电路,其特征在于,

所述输入阻抗匹配电路包含有源电感电路,用于匹配不同频率下的输入阻抗,所述有源电感电路包括:

第一NMOS晶体管,其源极连接第三电流源,漏极接电压源;

第二NMOS晶体管,其漏极连接第二电流源及所述第一NMOS晶体管的栅极;

第三NMOS晶体管,其漏极与所述第二NMOS晶体管的源极相连,栅极与所述第一NMOS晶体管的源极相连,源极接地:以及

第四NMOS晶体管,其漏极与所述第二NMOS晶体管的栅极以及第一电流源相连,栅极与所述第二NMOS晶体管的源极相连,源极接地;其中所述第一电流源连接电压源,用于向所述第四NMOS晶体管提供偏置电流:

所述放大电路与所述有源电感电路及所述输出阻抗匹配电路相连,其包含共源共栅结构的第五NMOS晶体管和第六NMOS晶体管,所述第五NMOS晶体管的栅极接所述低噪声放大器的信号输入端,所述第六NMOS晶体管的漏极接所述第一NMOS晶体管的源极及所述输出阻抗匹配电路的输入端以及第四电流源。

- 2.根据权利要求1所述的低噪声放大器,其特征在于,所述输入阻抗匹配电路还包含串联的第一电容与第一电阻,所述第六NMOS晶体管的漏极通过所述第一电容和所述第一电阻连接于所述第一NMOS晶体管的源极。

- 3.根据权利要求2所述的低噪声放大器,其特征在于,所述输入阻抗匹配电路还包含并联的第二电容和第二电阻,以及第七NMOS晶体管;其中所述第二电容和第二电阻连接于所述第五NMOS晶体管的栅极与所述第七NMOS晶体管的源极之间;所述第七NMOS晶体管的栅极与所述第六NMOS晶体管的漏极相连,源极连接第五电流源,漏极连接所述电压源。

- 4.根据权利要求3所述的低噪声放大器,其特征在于,所述输出阻抗匹配电路包含第八 NMOS晶体管,其栅极与所述第六NMOS晶体管的漏极相连,漏极接所述电压源,源极连接第六 电流源及所述低噪声放大器的信号输出端。

- 5.根据权利要求1所述的低噪声放大器,其特征在于,通过调节所述第二电流源和第三电流源改变所述有源电感电路的等效电感值,以匹配不同频率下的输入阻抗。

# 低噪声放大器

#### 技术领域

[0001] 本发明涉及集成电路领域,特别涉及一种低噪声放大器。

#### 背景技术

[0002] 低噪声放大器是射频收发机中的重要模块之一,主要用于通讯系统中将接收自天线的信号放大,以便于后级的接收机电路处理。

[0003] 由于来自天线的信号一般都非常微弱,低噪声放大器一般情况下均位于非常靠近天线的部位以减小信号损耗。正是由于噪声放大器位于整个接收机紧邻天线的最先一级,它的特性直接影响着整个接收机接收信号的质量。为了确保天线接收的信号能够在接收机的最后一级被正确的恢复,一个好的低噪声放大器需要在放大信号的同时产生尽可能低的噪音以及失真。

[0004] 随着现代移动通讯的发展,低噪声放大器要求能够适用于各种频率和协议的应用,因此对LNA的电感提出了更高的要求,尤其是要求LNA的电感可变,满足各种频率和协议应用的需要,从而使整个接收机成为一个宽带的接收机。输入端的阻抗匹配和噪声匹配是实现高增益和低噪声的关键,对输入端的阻抗匹配和噪声匹配影响最关键的是LNA的电感。 [0005] 通常来说,用于输入匹配的低噪声放大器电感是由无源器件所构成,这不仅要求集成电路制造工艺中支持电感工艺,即顶层和次顶层金属厚度非常大,而且由于电感占据了版图很多资源使得整个低噪声放大器的成本较高。

[0006] 因此,如果能够摆脱无源器件对工艺的专门要求、利用一种面积较小的有源电路来实现电感功能,将会对整个低噪声放大器的设计带来很大益处。

#### 发明内容

[0007] 本发明的主要目的在于克服现有技术的缺陷,提供一种具有较小面积的低噪声放大器。

[0008] 为达成上述目的,本发明提供一种低噪声放大器,其包括输入阻抗匹配电路、放大电路和输出阻抗匹配电路,其中所述输入阻抗匹配电路包含有源电感电路,用于匹配不同频率下的输入阻抗,所述有源电感电路包括:第一NMOS晶体管,其源极连接第三电流源,漏极接电压源;第二NMOS晶体管,其漏极连接第二电流源及所述第一NMOS晶体管的栅极;第三NMOS晶体管,其漏极与所述第二NMOS晶体管的源极相连,栅极与所述第一NMOS晶体管的源极相连,源极接地;以及第四NMOS晶体管的源极相连,漏极接地;所述放大电路与所述有源电感电路及所述输出阻抗匹配电路相连,其包含共源共栅结构的第五NMOS晶体管和第六NMOS晶体管,所述第五NMOS晶体管的栅极接所述低噪声放大器的信号输入端,所述第六NMOS晶体管的漏极接所述第一NMOS晶体管的源极及所述输出阻抗匹配电路的输入端以及第四电流源。

[0009] 优选的,所述输入阻抗匹配电路还包含串联的第一电容与第一电阻,所述第六

NMOS晶体管的漏极通过所述第一电容和所述第一电阻连接于所述第一NMOS晶体管的源极。 [0010] 优选的,所述输入阻抗匹配电路还包含并联的第二电容和第二电阻,以及第七 NMOS晶体管;其中所述第二电容和第二电阻连接于所述第五NMOS晶体管的栅极与所述第七 NMOS晶体管的源极之间;所述第七NMOS晶体管的栅极与所述第六NMOS晶体管的漏极相连,源极连接第五电流源,漏极连接所述电压源。

[0011] 优选的,所述输出阻抗匹配电路包含第八NMOS晶体管,其栅极与所述第六NMOS晶体管的漏极相连,漏极接所述电压源,源极连接第六电流源及所述低噪声放大器的信号输出端。

[0012] 优选的,通过调节所述第二电流源和第三电流源改变所述有源电感电路的等效电感值,以匹配不同频率下的输入阻抗。

[0013] 本发明的有益效果在于采用有源电感电路,使低噪声放大器具有低功耗、小面积、低成本等优点,此外,低噪声放大器的输入阻抗匹配电路通过利用偏置电流来调节晶体管的栅源寄生电容,即可改变有源电感电路的等效电感值,从而实现在宽频率范围内输入阻抗的匹配。

#### 附图说明

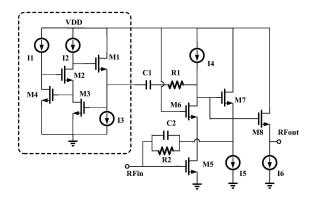

[0014] 图1为本发明一实施例低噪声放大器的电路示意图;

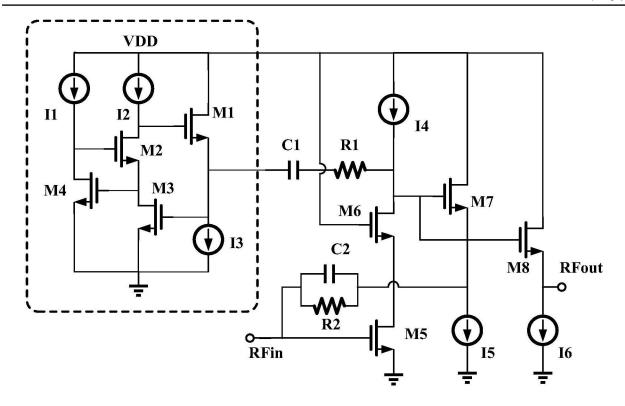

[0015] 图2为本发明一实施例低噪声放大器的有源电感电路的等效电路示意图:

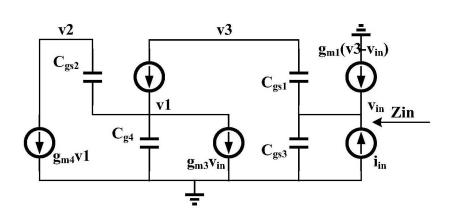

[0016] 图3为本发明一实施例低噪声放大器的输入匹配参数与频率关系的曲线图:

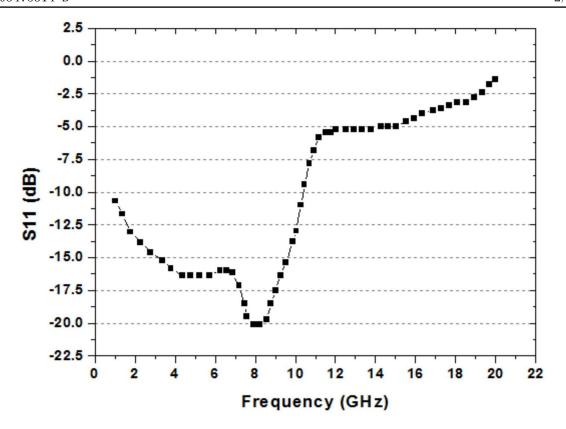

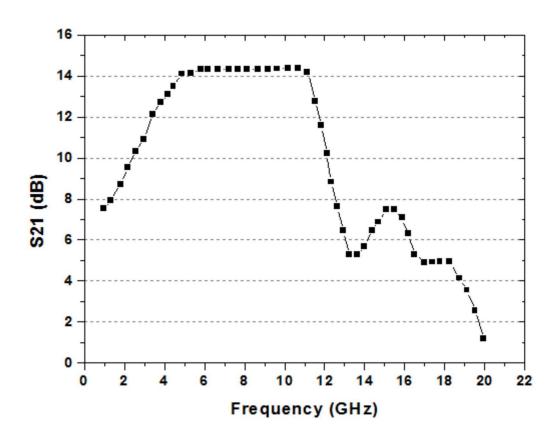

[0017] 图4为本发明一实施例低噪声放大器的输入匹配增益与频率关系的曲线图:

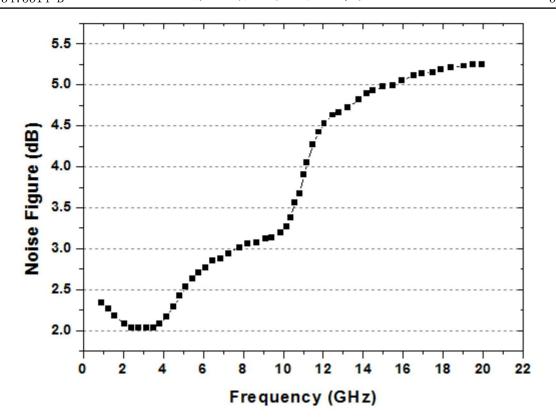

[0018] 图5为本发明一实施例低噪声放大器的噪声系数与频率关系的曲线图。

### 具体实施方式

[0019] 为使本发明的内容更加清楚易懂,以下结合说明书附图,对本发明的内容作进一步说明。当然本发明并不局限于该具体实施例,本领域内的技术人员所熟知的一般替换也涵盖在本发明的保护范围内。

[0020] 在本说明书中及在权利要求书中,应理解当一元件被称为"连接"到另一元件或与另一元件"相连"时,其可直接连接,或可存在介入元件。

[0021] 本发明的低噪声放大器包括输入阻抗匹配电路、放大电路和输出阻抗匹配电路,放大电路构成低噪声放大器的输入级,输出阻抗匹配电路构成低噪声放大器的输出级,输入阻抗匹配电路包括有源电感电路,其具有面积小、品质因子高、可控性好等特点。进一步的,本发明中,该有源电感电路的等效电感值可控,从而通过调节有源电感电路的等效电感值,就可以方便地调节该低噪声放大器的输入匹配,以使输入阻抗匹配电路实现低噪声放大器在不同工作频率下的输入阻抗均满足50欧姆的匹配要求。

[0022] 具体来说,请参考图1,该低噪声放大器的放大电路包括一对共源共栅(Cascode)结构的NMOS晶体管M5和NMOS晶体管M6,NMOS晶体管M5的栅极接信号输入端,NMOS晶体管M6的漏极接电流源I4,因此该共源共栅结构的偏置电流通过电流源I4来提供。

[0023] 输出阻抗匹配电路包括NMOS晶体管M8,其栅极连接NMOS晶体管M6的漏极,也即是放大电路的输出端,漏极接电压源VDD,源极接电流源I6以及信号输出端,电流源I6为NMOS

晶体管M8提供所需要的电流偏置。由图可知,输入的射频信号RFin通过低噪声放大器的输入级(即放大电路)放大以后,通过共源共栅晶体管M6的漏极将放大后的信号传输给NMOS晶体管M8的栅极,通过NMOS晶体管M8将信号进一步放大和缓冲之后,最终形成输出信号RFout。同时,由于该低噪声放大器的输出级为共漏结构,可以同时起到缓冲级的作用,低噪声放大器的输出匹配则通过调节NMOS晶体管M8的跨导gm和输出阻抗ro来实现。

[0024] 输入阻抗匹配电路中,有源电感电路包括NMOS晶体管M1、NMOS晶体管M2、NMOS晶体管M3、NMOS晶体管M4、电流源I1、电流源I2、电流源I3。其中,NMOS晶体管M1源极连接电流源I3,漏极接电压源VDD;NMOS晶体管M2漏极连接电流源I2及NMOS晶体管M1的栅极;NMOS晶体管M3漏极与NMOS晶体管M2的源极相连,栅极与NMOS晶体管M1的源极相连,源极接地;NMOS晶体管M4的漏极与NMOS晶体管M2的栅极及电流源I1相连,栅极与NMOS晶体管M3的源极相连,漏极接地。电流源I1连接电压源VDD,提供NMOS晶体管M4的偏置电流;电流源I2连接电压源VDD,提供NMOS晶体管M1的偏置电流;电流源I2连接电压源VDD,提供NMOS晶体管M1的源极为该有源电感电路的输入端,将其转换为图2所示的有源电感电路的等效电路图,从该输入端看到的阻抗即是这个有源电感电路的对地输入阻抗,为:

[0025]

$$z_{ind} = \frac{s}{C_{gs4}} \frac{s^2 + \frac{C_{gs4}}{C_{gs3}} \omega_4 s + \frac{g_{m4}}{g_{m3}} \omega_3 \omega_2}{s^4 + \omega_4 s^3 + \omega_4 \omega_2 s^2 + \omega_2 \omega_3 \omega_4 (s + \omega_1)}$$

[0026] 其中,

$$\omega_i = \frac{g_{mi}}{c_{asi}}$$

, $i=1,2,3,4$

[0027]  $Cgs1 \ Cgs2 \ Cgs3 \ ACgs4 \ DNMOS$ 晶体管M1、M2、M3和M4的栅源寄生电容,gm1、gm2、gm3和gm4为NMOS晶体管M1、M2、M3和M4的跨导,i<sub>in</sub>为输入端电流,Vin为输入端电压,V1为NMOS晶体管M4的栅极的对地电压;v2为NMOS晶体管M2的栅极的对地电压;V3对为NMOS晶体管M1的栅极的对地电压。在上式中,s=j $\omega$ =j2 $\pi$ f,f为该有源电感电路的工作频率,也即是低噪声放大器的工作频率。

[0028] 较佳的,当工作频率为低频,即当f较小时,上式可以进一步简化为:

[0029]

$$z_{ind}(j\omega_{low}) = \frac{sC_{gs1}}{\omega_1\omega_3} = j\omega L$$

[0030] 其中,低频频率范围为1GHz以下。

[0031] 由此,该有源电感电路的等效电感为:

[0032]

$$L = \frac{C_{gs1}}{\omega_1 \omega_3}$$

[0033] 因此,通过调节NMOS晶体管M1的栅源寄生电容Cgs1,就可以改变该有源电感电路的等效电感值,以更好地进行输入阻抗匹配。其中,栅源寄生电容Cgs1可通过直流源I2,I3进行调节。

[0034] 请继续参考图1,对于本实施例的低噪声放大器来说,输入阻抗匹配电路还包括电容C1、电阻R1、电容C2、电阻R2和NMOS晶体管M7,与有源电感电路共同形成50欧姆的输入匹配。如图1所示,电容C1与电阻R1串联,电容C1一端与有源电感电路的输入端,即NMOS晶体管M1的源极相连,电阻R1的一端与放大电路的输出端,即NMOS晶体管M6的漏极相连。电容C2和

电阻R2并联,一端连接低噪声放大器的输入端,另一端与NMOS晶体管M7串联。NMOS晶体管M7的漏极接电压源VDD,栅极连接放大电路的输出端,源极连接并联的电容C2和电阻R2以及电流源I5,由电流源I5向晶体管M7提供偏置电流。

[0035] 由于本发明的输入阻抗表达式繁琐,较难直观看出相对于传统低噪声放大器的优点,因此我们采用仿真实验加以验证。图3所示为本低噪声放大器的输入匹配参数S11与频率关系的曲线图。从图中可以看到,该低噪声放大器在频率1.1GHz~10.25GHz处的输入匹配S11都能够小于-10dB,也即意味着该低噪声放大器可以在1.1GHz~10.25GHz的宽频率范围内工作。

[0036] 图4所示为本低噪声放大器的增益S21与频率关系的曲线图。从图中可以看到,该低噪声放大器在4.8GHz~10.25GHz频率范围内达到增益S21最大值,该增益最大值超过了14dB。

[0037] 图5是本低噪声放大器的噪声系数NF与频率的关系曲线。从图中可以看到,该低噪声放大器在整个宽频率工作范围内,噪声系数可以达到最小值2.1dB,最大值小于3.5dB。该噪声系数可以满足多种频率下对低噪声放大器的要求。

[0038] 综上所述,相较于传统结构的低噪声放大器,本发明通过等效电感值可调的有源电感电路,不仅使得整个低噪声放大器具备非常小的面积,也可以实现低噪声放大器在不同工作频率下的输入阻抗的匹配。

[0039] 虽然本发明已以较佳实施例揭示如上,然所述诸多实施例仅为了便于说明而举例而已,并非用以限定本发明,本领域的技术人员在不脱离本发明精神和范围的前提下可作若干的更动与润饰,本发明所主张的保护范围应以权利要求书所述为准。

图1

图2

图3

图5